6. Sequential Logic¶

Most of today’s digital systems are build with sequential logic, including virtually all computer systems. A sequential circuit is a digital circuit whose outputs depend on the history of its inputs. Thus, sequential circuits have a memory that permits significantly more complex functional behaviors than combinational circuits are capable of. In fact, the study of the complexity of sequential circuit behavior is the cradle of the field of computer science.

6.1. Feedback Loops¶

We construct a sequential circuit by introducing a feedback loop. For example, we may connect the output of a combinational circuit to one of its inputs, as shown in Figure 6.1. This multiplexer circuit feeds output \(Y\) back to data input \(D_0.\) Because of this feedback loop, inputs of the past, in particular inputs that are arbitrarily older than the propagation delay of the multiplexer, can determine output \(Y.\) In the following, we analyze the circuit to derive a precise characterization of its behavior.

Figure 6.1: Multiplexer with feedback loop (left), and glitch-free implementation with consensus term \(X\) (right).

We may express the functionality of the multiplexer loop by means of the defining equation of the multiplexer, substituting \(Y\) for data input \(D_0\) and \(D\) for data input \(D_1\):

This definition is recursive, because \(Y\) appears as output on the lhs and as input on the rhs in case \(S=0.\) We interpret the recursion such that output \(Y\) follows input \(D\) if select input \(S\) equals 1, and holds output \(Y\) while \(S\) equals 0. Thus, when \(S=0\) the circuit retains the last value of input \(D\) before \(S\) transitions from 1 to 0. We know this behavior from the D-latch already. Now, we utilize the tools for combinational circuit design, including K-maps and timing analysis, to study the feedback loop in more detail.

First, we inspect the combinational portion of the multiplexer circuit without the feedback loop, and second we study the effects of the feedback loop. This separation of concerns is known as cut analysis:

- Cut all feedback loops, and rename all fed-back outputs that drive the loops.

- Analyze the combinational circuit by deriving the K-maps, called excitation table, for each fed-back output.

- Generate the transition table by marking all stable states in the excitation table, i.e. those K-map cells where the outputs driving the feedback loops equal the inputs driven by the feedback loops.

- Analyze the transitions of the sequential circuit in the presence of all feedback loops with the aid of the transition table.

We analyze the multiplexer circuit, starting with step 1 by cutting the feedback loop. Figure 6.2 illustrates the cut in the black-box diagram on the left and the combinational circuit implementing a glitch-free multiplexer on the right. We rename output \(Y\) that drives the feedback loop to \(Y',\) and keep name \(Y\) for the input of the multiplexer that is driven by the feedback loop.

Figure 6.2: Step 1 of cut analysis: cut the feedback loop, keep combinational input name \(Y,\) and rename the combinational output into \(Y'.\)

The resulting gate-level circuit of the multiplexer in Figure 6.2 is acyclic and, hence, combinational. Output \(Y'\) is a function of three inputs, \(D,\) \(S,\) and \(Y\):

The equivalent SOP form corresponding to the gate-level circuit is

Besides analyzing the functionality, we can analyze the timing of the combinational circuit, which resembles the analysis of the multiplexer without consensus term. Assume for simplicity that each gate has a propagation delay of 1 time unit, i.e. \(t_{pd}(inv) = 1,\) \(t_{pd}(and) = 1,\) and \(t_{pd}(or) = 1.\) Then, the multiplexer in Figure 6.2 has one path from \(S\) through the inverter with propagation delay \(t_{pd}(mux) = 3\) time units, and all other paths have contamination delay \(t_{cd}(mux) = 2\) time units. This completes our analysis of the combinational circuit.

According to step 2 of the cut analysis, we translate the multiplexer function into a K-map, also called excitation table, because it specifies the function of the circuit node that drives or excites the feedback loop. In case of the multiplexer circuit this node is \(Y'.\) Figure 6.3 shows the excitation table of \(Y'\) on the left. We have arranged variable \(Y\) to change across rows, because this simplifies step 3, determining the stable states for the transition table.

A circuit with a feedback loop is stable, if the output of the combinational circuit that drives the feedback loop is equal to the input of the combinational circuit driven by the feedback loop. After all, this is the purpose of the feedback wire to begin with: The feedback wire forces the voltage levels of the connected output and input of the combinational circuit to be equal. The stable states of our multiplexer loop are those cells in the excitation table where output \(Y'\) equals input \(Y.\) In Figure 6.3, the top row is associated with input \(Y=0.\) Therefore, the stable states are those cells of the top row marked with \(Y' = 0.\) Analogously, the bottom row is associated with \(Y=1,\) such that the stable states in the bottom row are all cells marked with \(Y' = 1.\) The excitation table with encircled cells identifying stable states is called transition table, see Figure 6.3 on the right. All remaining cells without circle identify unstable states. An unstable state is temporary, because output \(Y' \ne Y\) drives a new input \(Y'\) via the feedback loop into the combinational circuit.

We now use the transition table to pursue our original goal, the systematic analysis of the transitions of the multiplexer loop, i.e. step 4 of the cut analysis. The input terminals of the multiplexer loop in Figure 6.1 are data input \(D\) and select input \(S.\) We assume that the circuit is in a stable state, for example \((D,S,Y) = 100.\) This is the state associated the rightmost cell in the top row of the transition table, shown on the left in Figure 6.4 below. The loop holds output value \(Y' = 0\) indefinitely until we stimulate a transition by changing an input.

Figure 6.4: Transition paths of multiplexer loop stimulated by input change \(S: 0 \rightarrow 1\) (left) and then \(D: 1 \rightarrow 0\) (right).

Next, we change select input \(S\) from 0 to 1. In the transition table, we move by one cell to the left. This state is unstable, because output \(Y'=1\) differs from input \(Y=0.\) Input \(Y\) will assume output value 1 via the feedback loop after a delay of \(t_{cd} = 2\) time units, because inputs \((D,S)=11\) cause AND gate \(W\) to change from 0 to 1, which switches output \(Y'\) from 0 to 1. Therefore, the circuit transitions without further stimulus from unstable state \((D,S,Y)=110\) to state \((D,S,Y)=111.\) In the transition table, we move by one cell downward. State \((D,S,Y)=111\) is stable and produces output \(Y'=1.\) The same transition behavior occurs in a D-latch, after switching from opaque to transparent. The output follows input \(D\) such that \(Y'\) transitions from 0 to 1.

If we change data input \(D\) from 1 to 0 when the multiplexer loop occupies stable state \((D,S,Y)=111,\) the state transitions along the path illustrated in Figure 6.4 on the right. Since \((D,S,Y)=011\) is an unstable state, input \(Y\) will change to output \(Y'=0.\) Without further stimulus the circuit transitions to stable state \((D,S,Y)=010.\) The transition table enables us to argue about such transitions without inspecting the circuit diagram. Thus, the transition table is a powerful tool suited for tracing all possible transition paths in a circuit with feedback loops. In the transition table of the multiplexer loop, signal changes on the input terminals \(D\) or \(S\) correspond to transitions across columns within a row. State transitions due to the feedback loop start in an unstable state and cross rows within a column.

The transition table can be viewed as a simplifying abstraction of the timing diagram resulting from a timing analysis. The waveforms of the timing diagram provide the delays as additional information. Figure 6.5 shows the timing diagram of the transitions discussed in Figure 6.4 based on the signals of the multiplexer loop in Figure 6.1. Input transition \(S: 0 \rightarrow 1\) occurs at time \(t = 0,\) and input transition \(D: 1\rightarrow 0\) at time \(t = 6.\) Since we assume that each gate has a delay of 1 time unit, the transition of select input \(S\) takes a delay of \(t_{cd} = 2\) time units to produce a stable output \(Y=1,\) although it takes another time unit for the feedback loop to drive node \(X\) to value 1. Similarly, the transition of data input \(D\) takes \(t_{cd} = 2\) time units stabilize output \(Y=0.\)

Comparing the timing diagram with the transition tables in Figure 6.4, we observe that the multiplexer loop is in initial state \((D,S,Y)=100\) for \(t < 0.\) Then, we change select input \(S\) to 1, and the circuit is in unstable state \((D,S,Y)=110\) for time period \(0 < t < 2.\) At time \(t=2,\) output \(Y\) transitions to 1, and the circuit into stable state \((D,S,Y)=111.\) The multiplexer loop remains in this state until we provide the next input stimulus. This happens at time \(t=6,\) where we change data input \(D\) to 0. In time period \(6 < t < 8,\) the circuit occupies unstable state \((D,S,Y)=011,\) before it transitions into stable state \((D,S,Y)=010\) at time \(t=8.\) The transition table captures these transitions without the complexity of a timing analysis.

Using the transition table, we can study the behavior of the multiplexer loop when select input \(S = 0.\) Figure 6.6 shows on the left the transition starting in state \((D,S,Y)=010\) and changing \(S\) from 1 to 0. We move by one cell to the left into stable state \((D,S,Y)=000.\) Subsequently, we can change data input \(D\) from 0 to 1, transitioning the circuit to stable state \((D,S,Y)=100,\) and back, as shown in Figure 6.6 on the right. Output \(Y\) stores the last value of \(D,\) before we changed \(S\) from 1 to 0, no matter when and how often we toggle data input \(D.\) This timing behavior demonstrates the characteristic feature of sequential circuits: ouput \(Y\) depends on the history of inputs \(D\) and \(S.\) If \(D\) would have been 1 before we changed \(S\) from 1 to 0, the multiplier loop would have stored \(D=1\) by holding output \(Y = 1\) in stable states \((D,S,Y)=101\) or \((D,S,Y)=001.\)

Figure 6.6: Transition paths of multiplexer loop stimulated by input change \(S: 1 \rightarrow 0\) (left) and subsequently toggling \(D\) (right).

The distinction of stable and unstable states leads us to classify the behavior of entire sequential circuits with feedback as either stable or unstable. A sequential circuit is stable, if a change at an input terminal causes the circuit to transition from one stable state into another. Otherwise, if the outputs change beyond the propagation delay, the sequential circuit is unstable. We distinguish two types of unstable circuit. If the outputs become stable eventually, then the change of an input causes the circuit to transition through one or more unstable states into a stable state. If, however, the outputs change indefinitely, then the circuit must enter a cycle of transitions through unstable states. Unless we wish to design an oscillator, such a behavior is usually considered a bug. Transitions that are eventually stable but traverse unstable states are considered a harmless feature of sequential circuits, similar to glitches in combinational circuits.

We perform a cut analysis of the ring oscillator in Figure 6.7. The feedback loop connects output \(Y\) to the input of the NAND gate. We cut the feedback loop and rename output \(Y\) to \(Y'.\)

The combinational portion of the cyclic circuit is the 3-stage path NAND-INV-INV. The output function \(Y'(A,Y)\) is easily derived as follows. Since \(Y' = \overline{X} = W,\) we find \(Y' = \overline{A \cdot Y}.\) We may interpret the function of the NAND gate as

such that output \(Y'\) equals 1 if control input \(A=0,\) and \(Y'\) is the complement of input \(Y\) if \(A=1.\) Next, we translate this functionality into a K-map, and encircle the only stable state \((A,Y)=01\) to obtain the transition table below.

Based on the transition table we deduce the behavior of the ring oscillator. If input \(A=0,\) the circuit will eventually enter the stable state. If the circuit is in unstable state \((A,Y)=00,\) then output \(Y'=1\) enforces the transition into stable state \((A,Y)=01.\) If we change input \(A\) from 0 to 1, we move from the stable state by one cell to the right. State \((A,Y)=11\) is unstable. Since \(Y' = 0,\) it transitions after the propagation delay of the 3-stage path to state \((A,Y)=10,\) i.e. we move one cell up in the transition table. The resulting state \((A,Y)=10\) is unstable too. Output \(Y'=1\) forces the transition to state \((A,Y)=11,\) i.e. we move one cell down again. As long as input \(A\) remains 1, the circuit toggles between states \((A,Y)=10\) and \((A,Y)=11,\) and the output between \(Y'=0\) and \(Y'=1.\) The propagation delay between transitions is the delay of the 3-stage path. In other words, the oscillator produces a clock signal. To stop the oscillation, we change input \(A\) from 1 to 0, so that the circuit transitions into the stable state eventually. In the transition table, stimulus \(A: 1\rightarrow 0\) moves from the right to the left column, and if we are in the top row, then without further stimulus into the bottom row.

Not all combinational circuits with a feedback loop are sequential. There exist cyclic circuits whose outputs depend on the present inputs only rather than on the past inputs. An example of such a multioutput circuit is shown below.

We use a modified form of the cut analysis to show that this circuit is combinational. A circuit is sequential if we cut the feedback loop and the output driving the feedback loop is a function of the inputs driven by the feedback loop. If the output function of the driver of the feedback loop is independent of the feedback signal, then the feedback wire is redundant and the circuit is combinational.

Following this argument, we investigate whether output \(y_3\) of the circuit is sequential or combinational. We cut the feedback loop as shown below, and rename the output into \(y_3'.\)

Next, we deduce the Boolean expression for \(y_3'\) as a function of inputs \(x_0,\) \(x_1,\) and feedback input \(y_3,\) and simplify the expression to see whether \(y_3'\) depends on \(y_3\) or not:

We conclude that \(y_3'\) is not a function of feedback input \(y_3\) but is a function of terminal inputs \(x_0\) and \(x_1\) only. Therefore, \(y_3'\) depends on the present inputs \(x_0\) and \(x_1\) only, and is hence combinational.

Since the circuit is a multioutput circuit, it is combinational if all of its output functions are combinational. Therefore, we repeat the cut analysis for each output, cutting the loop at the input driven by the corresponding output. For example, to test \(y_0,\) we cut the loop at the \(y_0\)-input of the AND gate. Then, we find these expressions for the output functions:

None of the output functions depends on the feedback signal. Therefore, all output functions and the circuit as a whole are combinational. Intuitively, the complementation and covering theorems cause the feedback signal to vanish from the outputs. More interesting is the observation that this cyclic combinational circuit computes four distinct 2-variable functions with four gates, and is therefore competitive with four independent acyclic circuits.

Perform a cut analysis of the NAND loop:

- Cut the loop and rename the loop driver.

- Derive a K-map for the output (excitation table).

- Mark all cells with stable states (transition table).

- Analyze the transitions of the circuit.

Output \(Y\) of the NAND gate drives the feedback loop to its input. The first step of a cut analysis is to cut the feedback loop:

Then, we rename the loop driver, here \(Y \rightarrow Y',\) and redraw the resulting acyclic combinational circuit to enhance clarity:

The combinational circuit in (b) is easy to analyze: \(Y' = \overline{A\,Y}.\)

The excitation table of the loop circuit is the K-map of the acyclic combinational circuit, specified above by means of Boolean equation \(Y' = \overline{A\,Y}.\) Since the NAND operation produces \(Y' = 0\) only if both inputs are \(A = Y = 1,\) the corresponding K-map is:

We derive the transition table of the cyclic circuit with feedback loop from the excitation table of the acyclic circuit by marking all stable states that observe feedback constraint \(Y = Y'.\) The cells of the excitation table are marked with the associated value of output \(Y'.\) In the top row of the excitation table input \(Y = 0.\) However, both cells are marked with output \(Y' = 1.\) Thus, there are no stable states in the top row. In the bottom row of the excitation table input \(Y = 1.\) The leftmost cell is marked with output \(Y' = 1,\) which is equal to input \(Y.\) Therefore, this cell identifies the only stable state of the circuit.

We study the transitions of the NAND loop with the aid of the transition table. Input \(A\) is the only input of the NAND loop. Therefore, we first study the behavior of the circuit when \(A\) is fixed either to 0 or to 1, and then when input \(A\) changes.

Consider the case where input \(A = 0.\) We distinguish two cases depending on input \(Y.\) If \(Y = 1\) initially, then the circuit is in its stable state because output \(Y' = \overline{0\cdot 1} = 1\) of the NAND gate reinforces input \(Y = Y' = 1\) through the feedback loop. In the other case, input \(Y = 0\) initially. In the transition table below this initial state is associated with the top-left cell where \((A,Y) = 00.\)

State \((A,Y)=00\) is unstable, because output \(Y'=1\) of the NAND gate drives input \(Y=Y'=1\) through the feedback loop, which differs from the initial state \(Y=0.\) Thus, the feedback loop transitions the circuit into new state \((A,Y)=01.\) This is the stable state of the circuit associated with the bottom-left cell. After transitioning into the stable state, the circuit has stabilized. We conclude that the circuit stabilizes when input \(A=0\) such that output \(Y'=1\) eventually.

Next, we consider case \(A=1.\) If input \(Y=0\) initially, the circuit is in state \((A,Y)=10\) associated with the top-right cell of the transition table. Since the output of the NAND gate produces \(Y'=1,\) the feedback loop enforces the input transition \(Y: 0\rightarrow 1.\) The circuit transitions to state \((A,Y)=11\) associated with the bottom-right cell of the transition table.

In the other case, where input \(Y=1\) initially, the circuit is in state \((A,Y)=11.\) This state is unstable, because output \(Y'=0\) of the NAND gate enforces the input transition \(Y: 1\rightarrow 0\) through the feedback loop. Thus, the circuit transitions to state \((A,Y)=10.\) We conclude that the circuit oscillates when input \(A=1,\) like the ring oscillator of Example 6.1.

Changes at input \(A\) transition the circuit between stable state \((A,Y) = 01\) and the oscillating behavior when input \(A=1.\) The exact state sequence of the transition depends on the state of the circuit when \(A\) transitions. In particular, if the circuit oscillates when \(A\) changes from 1 to 0, input \(Y\) assumes one of the two values 0 or 1 beyond our control. If \(Y\) happens to be 1, then state transition \((A,Y): 11 \rightarrow 01\) assumes the stable state immediately. On the other hand, if \(Y\) happens to be 0 when \(A\) changes from 1 to 0, then the state transitions through unstable state 00 into stable state 01, i.e. \((A,Y): 10 \rightarrow 00 \rightarrow 01.\) The inverse input transition \(A: 0\rightarrow 1\) causes the circuit to oscillate, most likely originating in stable state \((A,Y) = 01,\) because unstable state \((A,Y)=00\) transitions into the stable state when \(A=0.\)

6.2. Synchronous Circuits¶

Feedback is the key to processing past and present information of an input sequence. Memory elements, including the D-latch and the D-flipflop, are sequential circuits with feedback loops. In general, it is nontrivial to design a sequential circuit by augmenting a combinational circuit with feedback loops, because the delays of such loops are difficult to control and the timing behavior of compositions is hard to analyze. Even worse, hazards are difficult to predict in compositions of subcircuits with feedback loops, and potentially cause the circuit to become unstable indefinitely and malfunction. Nevertheless, sequential circuits with feedback loops are of interest per se, and design methodologies have been developed to cope with the problems of this class of circuits, widely known as asynchronous circuits today. The D-latch and the D-flipflop are asynchronous sequential circuits whose design has benefited from these developments.

Another circuit style dominates today’s digital design practice, known as synchronous circuits. The name derives from the introduction of a chronometer or clock signal that is used to trigger all D-flipflops of a circuit at the same beat of the clock. Furthermore, in an effort to simplify the control of delays through feedback loops, we insert a D-flipflop in every feedback loop. Since D-flipflops are edge-triggered memory elements, their outputs are stable for an entire clock period. When placed in a feedback loop, the output of the D-flipflop is the feedback input for the combinational circuit. Other than in an asynchronous circuit, the D-flipflop keeps the feedback input stable during the clock period. Hence, the loop cannot become unstable and can even tolerate hazards in the combinational logic, provided the clock period is larger than the combinational propagation delay.

The design style of synchronous circuits radically restricts the overall design space for sequential circuits. Nevertheless, it simplifies the task of circuit design dramatically, and is still powerful enough to assemble reliable circuits with billions of transistors. As such the synchronous design style is part of the unique success story of large scale digital systems engineering. Given their practical importance, we focus the remainder of this chapter on synchronous sequential circuits. This section discusses an analysis methodology for synchronous sequential circuits and introduces three sequential building blocks, a binary counter, shift registers, and memories.

6.2.1. Analysis of Synchronous Sequential Circuits¶

We demonstrate the functional analysis of synchronous sequential circuits by means of the multiplexer loop, extended with a D-flipflop in the feedback loop. As shown in Figure 6.8, D-flipflop output \(Q\) drives the feedback input of the multiplexer, and clock signal \(\phi\) triggers the D-flipflop at the positive clock edge. At this point in time the D-flipflop stores its input \(Y\) for an entire clock cycle until the next positive clock edge occurs.

The value stored in the D-flipflop is called the state of the synchronous circuit. In Figure 6.8 the state is observable at D-flipflop output \(Q.\) The purpose of circuit analysis is to determine the next state of the next clock cycle. If we consider all possible input combinations, the analysis enables us to predict the sequence of output values given a sequence of input values. The next state of the multiplexer loop is the value of input \(Y\) of the D-flipflop at the time of the triggering clock edge. Signal \(Y\) is driven by the combinational multiplexer circuit, and is a function of inputs \(D\) and \(S,\) and state \(Q\):

We use an adapted form of transition table, the so-called state transition table, to list the next state as a function of the state and the inputs. Since the state of the circuit is equal to \(Q\) and the next state is equal to \(Y,\) the state transition table of the multiplexer loop in Figure 6.8 is:

state (\(Q\)) \(D\) \(S\) next state (\(Y\)) 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 1 1 0 1 0 1 1 0 1 1 1 1 1

State transition tables are commonly drawn in form of a truth table, although we could use the equivalent K-map form as well. Under the assumption that the input values \(D\) and \(S\) are stable at the time of the triggering clock edge, we derive next state \(Y\) by evaluating equation \(Y(D,S,Q)\) for the combination of input values in each row. This equation specifies the next state logic implemented by the combinational multiplexer.

Although the state transition table specifies the transition behavior of a sequential circuit unambiguously, it can be advantageous to visualize the transition behavior by means of a directed graph, the so-called state transition diagram. Here, each vertex represents a state, and each arc a transition. We annotate the arcs with the combination of input values associated with the state transition. Separated by a slash, we also include output \(Y\) of the circuit, which happens to be equal to the next state in this example. Figure 6.9 shows the state transition diagram of the multiplexer loop in Figure 6.8. The vertices are marked with the value of state \(Q.\) The format of the arc annotations is \((D,S)/Y,\) i.e. the pair of input values followed by a slash followed by the output value.

Figure 6.9: State transition diagram of synchronous multiplexer loop. Arcs are marked with input and output values, separated by a slash.

We interpret the state transition diagram as follows. During the present clock cycle, the circuit is in one of the states represented by a vertex, for example in state 0. While in this state, the inputs may change causing the output to change. For example, in state 0, if we apply inputs \((D,S)=01,\) then output \(Y=0,\) as indicated by arc annotation \(01/0.\) If we apply inputs \((D,S)=11,\) then output \(Y=1,\) and the arc annotation is \(11/1.\) The input combination at the time of the triggering clock edge determines the next state. For example, arc \(11/1\) points from state 0 to state 1, because at the triggering clock edge next state \(Y=1\) is stored in the D-flipflop. The other three input combinations \(00/0,\) \(01/0,\) and \(10/0\) store next state \(Y=0\) at the triggering clock edge, which is also the present state. Therefore, the corresponding arc is a loop from state 0 to state 0 for all three input combinations. Comparison with the next state table shows that each arc annotation in the diagram corresponds to one row in the table. The diagram captures the transition behavior in a more compact form, that some designers find easier to comprehend than a table.

The state transition table and/or the state transition diagram enable us to derive the output sequence of the circuit if the inputs are synchronized with the clock, such that during each clock cycle one new pair of inputs arrive. For example, assume that the multiplexer loop is initially in state 0, and we apply the input sequence 00, 11, 10, 01, 10. Then, the corresponding output sequence is 0, 1, 1, 0, 0. Here is why. Initially, the circuit is in state 0, and we apply the first input pair 00. Hence, the output is \(Y=0.\) At the next triggering clock edge, the D-flipflop stores next state 0. Now, we apply the second input pair 11. The output changes to \(Y=1.\) At the next triggering clock edge the circuit transitions to state 1. The third input pair 10 holds output \(Y=1,\) and so on. Use the interactive model in Figure 6.10 to develop a feeling for the synchronous multiplexer loop. You can toggle inputs \(D\) and \(S\) and trigger a positive clock edge by pushing the \(\phi\) trigger button.

D = 0 S = 0 Figure 6.10: Interactive model of synchronous multiplexer loop.

The multiplexer loop does not restrict the inputs to change only once per cycle. In fact, you can change inputs \(D\) and \(S\) as often as you like between triggering clock edges. The output follows the inputs through the combinational logic implemented by the multiplexer. State changes, however, occur only upon triggering a positive clock edge. At this time, the D-flipflop stores the next state supplied to its input by multiplexer output \(Y.\) In summary, if input \(S=1,\) the loop stores input \(D\) at the time of the clock trigger. Otherwise, while \(S=0,\) the loop holds its state across clock trigger events independent of \(D.\) The state transition table and diagram above contain the same information about the circuit.

In the following, we analyze several synchronous sequential circuits by deriving their state transition table and diagram. These circuits are sequential building blocks for the design of larger sequential circuits.

6.2.2. Binary Counter¶

An \(n\)-bit binary counter is a synchronous sequential circuit that increments its \(n\)-bit output \(Y\) at every triggering clock edge. Since \(n\) bits can represent unsigned numbers in range \([0, 2^n-1],\) the counter rolls over to 0 when incrementing the largest value \(2^n-1\) of the representable number range. Therefore, \(n\)-bit binary counters are also called modulo-\(2^n\) counters. Figure 6.11 shows a 3-bit binary counter with a reset input to force the counter to zero. While the reset input is 0, the reset signal is inactive. Whenever a positive clock edge occurs the counter increments the value stored in the 3-bit register. If the reset input is equal to 1 during a positive clock edge, the register is reset to zero.

reset = 0 Figure 6.11: Interactive model of a 3-bit binary counter.

The counter circuit is synchronous, because the feedback loop contains a clock triggered register. Output \(Y\) of the register feeds back into the 3-bit adder. The second input of the adder is hardwired to constant value \(1_{10}.\) We tacitly assume that the carry-in of the adder is grounded to value 0, and the carry-out is unused. Sum output \(S\) of the adder generates the 3-bit sum \(S=(Y+1) \bmod 8.\) Recall that the largest unsigned binary number representable with 3 bits is \(2^3-1 = 7_{10},\) and \(7+1=8_{10} = 1000_2\) requires 4 bits. Since the sum output of the adder excludes the most significant carry-out bit, we obtain \(S = 000_2 = 0_{10}\) for input \(Y=7_{10}.\) The multiplexer implements the reset logic. Next state signal \(Y'\) is the output of the combinational portion of the feedback loop, and obeys the multiplexer logic:

We analyze the behavior of the counter circuit by deriving the state transition diagram. The circuit has one input besides clock \(\phi,\) i.e. the reset signal, and one output, which is counter value \(Y.\) First assume that the reset signal is inactive, and the counter increments its output at every positive clock edge. During a clock cycle the register stores the present state and drives it on output \(Y,\) where we can observe the state. At the next positive clock edge, the circuit transitions to next state \(Y'.\) We draw the state transition diagram, we need to start with some state, for example state \(0_{10}.\) We represent the state with a new vertex and mark it with its identifying state value 0. The next state of state \(0_{10}\) is \(Y'=1_{10}.\) We draw a second vertex, mark it with state value \(1_{10},\) and draw an arc from vertex 0 to vertex 1.

Figure 6.12: State transition diagram of 3-bit binary counter. Arcs are marked with input values only. Vertices are augmented with the output values.

Rather than annotating the arc with the output value as we did in Figure 6.9, we annotate the vertices with the output values. The reason for this change is a subtle difference in the output behavior of the circuits. In the multiplexer loop of Figure 6.8 the combinational logic drives the output whereas in the counter loop of Figure 6.11 the register drives the output. Whereas the output of the multiplexer loop depends on the present inputs, this is not the case for the binary counter. Output \(Y\) of the binary counter is stable during the entire clock cycle, independent of the reset input. The output changes only at the positive clock edge. In the state transition diagram in Figure 6.12 we emphasize this behavior by marking arcs with the input value of the reset input, and augment the state vertices with the output value.

As long as the reset input is 0, the counter circuit transitions from state \(Y\) to state \((Y+1) \bmod 8\) at each triggering clock edge. Thus, the state transition graph is a single cycle with eight states. If the reset input is 1, however, the counter transitions to state 0, independent of the present state. The reset arcs form additional cycles in the state transition diagram. As shown in Figure 6.12, the complete diagram has nine cycles. We could join the output arcs of state 7, however, because both input values 0 and 1 cause a transition to state 0.

The state transition table is the equivalent representation of the state transition diagram in Figure 6.12. For the binary counter, it assumes the form of a truth table with one column for the present state and the reset signal as inputs, and the next state as output. Frequently, designers augment the state transition table with the output specification, here with one column for output \(Y\):

state reset next state output 0 0 1 0 0 1 0 0 1 0 2 1 1 1 0 1 2 0 3 2 2 1 0 2 3 0 4 3 3 1 0 3 4 0 5 4 4 1 0 4 5 0 6 5 5 1 0 5 6 0 7 6 6 1 0 6 7 0 0 7 7 1 0 7

In case of the binary counter, specifying output \(Y\) in the state transition diagram or table is redundant, since the state and the output are equal. This is not the case in general, however. Note that we can deduce from the state transition table that the output is driven by the register rather than the combinational logic, because the output equals the present state, independent of the reset input.

6.2.3. Shift Register¶

An \(n\)-bit shift register has one serial input and \(n\) parallel outputs. Its function can be described as a serial-to-parallel converter. Figure 6.13 shows a 4-bit shift register with serial input \(S_{in}\) and four parallel outputs \(Y_i,\) where \(0 \le i < 4.\) Some implementations provide parallel output \(Y_{n-1}\) also as a separate serial output \(S_{out}.\) At each positive clock edge, the state is shifted by one D-flipflop to the right. After shifting four bits during four consecutive clock cycles into the shift register, all four bits are available at the parallel outputs. Considering the serial input and serial output only, the shift register implements a FIFO, short for first-in-first-out buffer. The first of multiple bits shifted in at \(S_{in}\) is the first bit to be shifted out at \(S_{out}.\) It takes four clock cycles for a bit to propagate through the FIFO.

Sin = 0 Figure 6.13: Interactive model of a 4-bit shift register.

The shift register is a synchronous sequential circuit, although the circuit diagram does not show any loops. The feedback loops are hidden inside the D-flipflops. In essence, a shift register is a series composition of D-flipflops, all triggered by the same clock signal. The state of the shift register can be observed at the outputs as binary number \(Y_3 Y_2 Y_1 Y_0.\) Figure 6.13 enables you to derive the state transition table of the 4-bit shift register:

state \(S_{in}\) next state output 0 0 0 0000 0 1 8 0000 1 0 0 0001 1 1 8 0001 2 0 1 0010 2 1 9 0010 3 0 1 0011 3 1 9 0011 4 0 2 0100 4 1 10 0100 5 0 2 0101 5 1 10 0101 6 0 3 0110 6 1 11 0110 7 0 3 0111 7 1 11 0111 8 0 4 1000 8 1 12 1000 9 0 4 1001 9 1 12 1001 10 0 5 1010 10 1 13 1010 11 0 5 1011 11 1 13 1011 12 0 6 1100 12 1 14 1100 13 0 6 1101 13 1 14 1101 14 0 7 1110 14 1 15 1110 15 0 7 1111 15 1 15 1111

The state transition table confirms that the outputs are independent of input \(S_{in}.\) This is no surprise, because the outputs are driven by the D-flipflops. Besides, the shift register has no combinational logic other than wires. Therefore, when drawing the corresponding state transition diagram we associate the output with a state vertex and the value of input \(S_{in}\) with an arc, analogous to the state transition diagram of the binary counter in Figure 6.12. We leave it as an exercise to translate the state transition table into a state transition diagram. You may view the resulting state transition diagram as a directed graph, and find the shortest paths to transition from one state to another in order to minimize the number of clock cycles and the length of the serial input sequence. For example, given state 6 you need at least two cycles to transition to state 9. The path transitions through state 3 by first applying serial input 0 and then 1.

We can extend the shift register to function not only as a serial-to-parallel converter but also as a parallel-to-serial converter. To that end, we provide parallel data inputs and include a multiplexer at each D-flipflop input. Figure 6.14 shows the extended 4-bit shift register. The Load input selects the multiplexer inputs between the parallel data inputs \(D_i,\) \(0 \le i < 4,\) and the original serial inputs. When Load equals 1 at the triggering clock edge, all D-flipflops store the values provided at the parallel data inputs. Otherwise, when Load equals 0, the circuit performs a right shift. During each clock cycle, the circuit outputs the data serially, bit-by-bit, at output \(S_{out}.\)

The shift register in Figure 6.14 can be used to implement the ports of a serial communication channel, such as RS-232. The sender uses the parallel-to-serial functionality to load a byte of data into the shift register, and transmit the byte serially across one wire to a receiver. The receiver shifts the bits serially into its shift register, and outputs the byte in parallel, using the serial-to-parallel functionality.

6.2.4. Memories¶

The memory elements discussed so far, including the D-flipflop, are relatively fast circuits but require more transistors than necessary to store a single bit. The hallmark of memory circuits is their density, i.e. the number of bits stored per unit of chip area.

Memory Organization¶

There exist serveral different technologies to implement a 1-bit memory element. However, independent of the technology virtually all memory architectures consist of a 2-dimensional array of such 1-bit memory elements, also called bit cells in this context. Figure 6.15 shows the block diagram of a \(4\times 3\) array of bit cells.

The array has an address bus \(A\) as input, and a data bus \(D\) as input and output. In general, \(n\)-bit address \(A\) drives an \(n{:}2^n\)-decoder to assert one of \(2^n\) wordlines, thereby selecting one row of the array of bit cells. We call a group of \(m\) data bits a word, and consider a word the unit of data transfer in and out of the memory array. In order to read one word out of one row of bit cells, we apply the associated binary-coded address, and the \(m\)-bit data bus outputs the word via the bitlines. If we want to write a word into the memory, we drive the word onto the bitlines, and apply the desired address.

Each bit cell is responsible for implementing a tristate behavior depending on the select input driven by the wordline and the signal on the bitline. Figure 6.16 shows one bit cell with its select input \(S\) connected to the wordline and data port \(D\) connected to the bitline for input and output. If the wordline drives a 0 on select input \(S,\) the cell disables data port \(D,\) indicated by value \(Z\) in Figure 6.16. As a result the cell is invisible to the bitline. Otherwise, if the wordline drives a 1 on select input \(S\) the cell is enabled. The enabled cell performs a read or write operation depending on the state of the bitline. In order to write the cell, we use a tristate buffer to drive the desired value onto the bitline. This data input is enabled with signal \(D_{en}.\) While \(D_{en} = 1,\) the tristate buffer drives data input \(D_{in}\) onto the bitline, and writes \(D_{in}\) into the enabled cell. On the other hand, if \(D_{en}=0,\) the data input is disabled, and the enabled cell makes its stored bit visible to the bitline, where we can observe it at data output \(D_{out}.\)

wordline = 0 Den = 0 Din = 0 Figure 6.16: Interactive model for reading and writing a bit cell.

When multiple rows of bit cells are arranged in an array, all cells in a column are connected to the same bitline. To read one word from the array, at most one row may make its stored bits visible on the bitlines. The cells in all other rows must disable their data ports. Figure 6.17 illustrates the interplay of the rows in an array when reading one row. Note that the address decoder guarantees that at any point in time exactly one row of cells is enabled, because the decoder drives a one-hot encoding of the binary address onto the wordlines.

A1 = 0 A0 = 0 Figure 6.17: Interactive model for reading a 4x3 memory array.

Memory Technologies¶

If a memory cannot be written but read only, like the memory array in Figure 6.17, it is called read only memory, or ROM for short. ROMs are nonvolatile memories because they retain their data if the power supply is switched off. Historically, data were stored irreversibly in a ROM by burning a fuse in each bit cell. Most ROMs today are programmble ROMs or PROMs that can be written once. Popular examples for PROMs are CDs and DVDs. A memory that can be read and written is called random access memory or RAM. A RAM is a volatile memory that loses its data when the supply power is switched off. The name random access is historically motivated to distinguish a RAM, where each bit is assumed to have the same access time, from sequential access memories like tapes, where a bit is located in a particular position on the tape, and the mechanical winding of the tape into the bit position determines its access time. Today, two types of semiconductor RAMs are wide spread, the DRAM and the SRAM. We briefly introduce these two types of RAMs by discussing their characteristic bit cell technologies.

A dynamic RAM, or DRAM for short, stores a bit in form of charge on a capacitor. Figure 6.19 shows the DRAM bit cell consisting of the capacitor and an nMOS transistor. If the capacitor is discharged to GND, we interpret the bit stored in the cell as logical 0. Otherwise, if the capacitor is charged to \(V_{DD},\) we interpret the stored bit as logical 1. The nMOS transistor controls the cell. If the wordline is 1, the nMOS transistor enables the cell by connecting the capacitor to the bitline. Otherwise, if the wordline is 0, the nMOS transistor is switched off, and disables the cell by disconnecting the capacitor from the bitline.

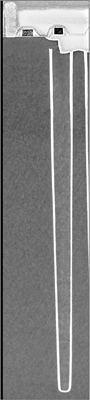

When reading the DRAM bit cell, the nMOS transistor connects the capacitor to the bitline. If the capacitor is discharged, we observe a zero voltage at the data output of the bitline. Otherwise, the charge of the capacitor diffuses onto the bitline, and we observe a logical 1 at the data output. Since the charge diffuses due to reading, we need to restore the bit cell after reading it. This is the reason why a DRAM is called dynamic RAM. Restoring the bit cell simply means writing the read value by driving it onto the bitline again, see Figure 6.16. The capacitor must be large enough so that a positive charge can be detected at the data output of the bitline. Figure 6.18 shows a deep trench capacitor, where a deep hole is drilled into a silicon wafer that is filled with metal. Since real capacitors leak, the charge stored on the capacitor must be restored periodically or the bit is lost.

The SRAM is a static RAM where the bit cell is stable because its state is continuously replenished by the power supply. An SRAM cell is essentially a bistable inverter pair. As shown in Figure 6.20, we control the inverter pair with two nMOS transistors and extend the memory array with a complemented bitline. Since each CMOS inverter requires two transistors, the bit cell as a whole consists of six transistors (6T). When the wordline is 0, the nMOS transistors disconnect the inverter pair from the bitlines. Otherwise, the bitlines are connected to the complemented and uncomplemented bit \(Q\) stored in the cell. We read the bit of the enabled cell at the data outputs of the bitlines. Writing a bit requires drivers at the data inputs of the bitlines that are stronger (larger) than the inverters of the cell, so as to overpower the inverter pair into the desired state.

DRAM and SRAM memories are sequential circuits. However, neither memory design requires a clock signal for its operation. Therefore, DRAMs and SRAMs are asynchronous sequential circuits in principle. To operate within a synchronous design, memory arrays are wrapped into synchronous control logic to ensure that the read and write operations stabilize within a clock cycle. Figure 6.21 shows a black-box synchronous memory module. It has a clock input, a write-enable input WE, an \(n\)-bit address input, and an \(m\)-bit data input and \(m\)-bit data output.

The read operation of a synchronous memory module is considered a combinational operation, independent of the triggering clock edge. Reset the WE input to 0, apply the desired address \(A,\) and the associated data word appears at data output \(D_{out}\) after the propagation delay within one clock cycle. In contrast, the write operation is synchronized by the clock. Set the WE input to 1, apply the desired address \(A\) and data input \(D_{in},\) and the data is written into memory at the triggering positive clock edge.

The bus width of the address input specifies the number of rows, also called depth, of the memory array. Given \(n\) address wires, the \(n{:}2^n\) address decoder drives \(2^n\) wordlines, as shown in Figure 6.15, so that the depth of the memory array is \(2^n.\) The bus width of the data input and the data output is equal to the number of columns, also called width or word size, of the memory array. Thus, the memory array inside the synchronous memory module in Figure 6.21 has a width of \(m.\) The capacity of a memory is the number of bit cells, i.e. depth \(\times\) width bits. The memory array in Figure 6.15, for example, has 2 address bits, a depth of \(2^2 = 4,\) a width of 3, and a capacity of \(4 \times 3 = 12\) bits.

Logic in Memories¶

Memories serve not only their purpose as a storage medium but are also used as universal logic operators. Given a \(n\)-variable logic function, we use a \(2^n \times 1\) memory array with \(n\) address inputs and one data output as a lookup table to read the function values. We can configure a RAM to implement any logic function by storing one function value per row. Essentially, the memory stores the truth table of a given combinational function and we select the row by applying the desired input combination. Figure 6.22 shows a 2-input XOR function \(Y = A \oplus B,\) implemented by means of a \(4\times 1\) memory array.

A = 0 B = 0 Figure 6.22: 2-input XOR gate implemented with a \(4\times 1\) memory array.

Memories can implement multioutput functions by including one column per output. Thus, a multioutput function with \(m\) outputs can be realized with a memory array of width \(m.\) Since RAMs permit configuring any multioutput function that fits the depth and width of the memory array, RAMs serve as lookup tables in reconfigurable logic devices, including FPGAs.

Analyze the synchronous sequential NAND loop.

- Derive the next-state logic.

- Derive a state transition table.

- Derive a state transition diagram.

- Use a time table to analyze the transitions of input sequence \(A = \langle 0, 0, 1, 0, 0, 0, 1, 1, 1, 1 \rangle.\)

The sequential NAND loop has a register on the feedback path. The state of the present clock cycle is observable at register output \(Q.\) The next state is the value of the data input of the register, and is stored at the next positive clock edge. In the NAND loop, the next state equals output \(Y,\) and is a function of present state \(Q\) and input \(A\):

\[Y(A,Q) = \overline{A Q}\,.\]This function is the combinational next state logic of the circuit.

The state transition table is the truth table of the next state logic:

\(A\) \(Q\) \(Y\) 0 0 1 0 1 1 1 0 1 1 1 0 The state transition diagram is the graphical representation of the state transition table. It has one vertex per state, here \(Q \in \{ 0, 1 \},\) and one arc per transition. We annotate the arcs with input \(A\) and output \(Y,\) separated by a slash. Note that output \(Y\) is also the next state of the NAND loop.

The diagram shows that the NAND loop transitions from state \(Q=0\) to state \(Q=1\) regardless of input \(A.\) Thus, when the circuit transitions into state \(Q=0,\) it remains there for one clock cycle before returning to state \(Q=1.\) It remains in state \(Q=1\) while input \(A=0,\) and transitions to state \(Q=0\) when input \(A=1.\) If we hold input \(A\) at value 1, the circuit toggles between states 0 and 1 at every positive clock edge. This behavior resembles the oscillation in Exercise 6.1.

We use a time table to study the behavior of the NAND loop over time given input sequence \(A\) for ten clock cycles, \(0 \le t < 10\):

t 0 1 2 3 4 5 6 7 8 9 Q X 1 1 0 1 1 1 0 1 0 A 0 0 1 0 0 0 1 1 1 1 Y 1 1 0 1 1 1 0 1 0 1 We do not need to know initial state \(Q[0]\) during clock cycle \(t = 0\) to conclude that next state \(Y[0]=1\) if \(A=0.\) Therefore, we mark \(Q[0] = X\) as unspecified. While \(A=0,\) the circuit stays in state 1, and toggles between states 0 and 1 while \(A=1.\)

6.3. Finite State Machines¶

Finite state machines, or FSMs for short, are a subset of synchronous sequential circuits with a finite number of states. Although state machines with infinitely many states are of minor practical relevance, the distinction hints at the theoretical importance of FSMs as an abstract model for the study and design of sequential circuits.[1] In this section, we discuss FSMs and their use as a design methodology for synchronous sequential circuits.

6.3.1. Mealy and Moore Machines¶

Our study of synchronous circuits has revealed nuances in the behavior of such circuits. In particular, the multiplexer loop has an output which is a function of the input and the state, whereas the output of the binary counter is a function of the state only. Since the output of the multiplexer loop is a function of the input, the output may change during a clock cycle if the input changes. In contrast, the output of the binary counter remains stable during the clock cycle. We exploit this difference by tailoring the annotations in the state transition diagrams of Figure 6.9 and Figure 6.12 to their respective needs. In fact, these circuits examplify two distinct types of synchronous sequential circuits.

Machine Models¶

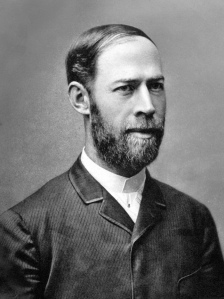

FSMs are generalizing models of synchronous sequential circuits. Figure 6.23 shows the Mealy machine model, named after George H. Mealy, and Figure 6.24 shows the Moore machine model, named after Edward F. Moore. Both machines have

- input bus \(I\) with \(m \ge 0\) signals \(I_0, I_1, \ldots, I_{m-1},\)

- output bus \(O\) with \(n \ge 0\) signals \(O_0, O_1, \ldots, O_{n-1},\)

- current state \(S\) stored in a \(k\)-bit state register with output signals \(S_0, S_1, \ldots, S_{k-1},\) \(k > 0,\) and capable of encoding up to \(2^k\) distinct states,

- next state \(S'\) with \(k\) signals \(S'_0, S'_1, \ldots, S'_{k-1},\)

- combinational next state logic \(\sigma,\) and

- combinational output logic \(\omega.\)

The next state logic of both Mealy and Moore machines is a combinational function \(\sigma: \mathcal{B}^{m+k}\rightarrow \mathcal{B}^k\) that computes next state \(S' = \sigma(S,I).\) The next state computation receives the present or current state \(S\) via the feedback loop. The loop includes the state register triggered by clock signal \(\phi,\) which qualifies both machines as synchronous sequential circuits.

The essential difference between the two machine models is the combinational output logic \(\omega.\) For the Mealy machine, output function \(\omega: \mathcal{B}^{m+k} \rightarrow \mathcal{B}^n\) computes output \(O = \omega(S,I)\) as a function of current state \(S\) and input \(I.\) In contrast, the output function of the Moore machine \(\omega: \mathcal{B}^k \rightarrow \mathcal{B}^n\) computes output \(O = \omega(S)\) as a function of current state \(S\) only. The only difference in the circuit diagrams is that the Mealy machine connects input terminal \(I\) to combinational output logic \(\omega\) whereas the Moore machine does not. As a matter of convention for this chapter, we distinguish combinational and sequential logic in circuit diagrams by drawing black-box subcircuits of combinational logic as rectangles with round corners.

Machine Identification¶

It is not always immediately obvious which type of machine, Mealy or Moore, a synchronous sequential circuit implements. In fact, it may take several attempts of restructuring a circuit before it fits the structure of the Mealy machine in Figure 6.23 or the Moore machine in Figure 6.24. However, the distinguishing characteristic is usually straightfoward to check, i.e. whether the output is a function of the input or not. Consider the multiplexer loop in Figure 6.8, for example. Output \(Y\) is a function of state \(Q\) and inputs \(D\) and \(S.\) Therefore, the circuit is a Mealy machine. But, what is its next state logic \(\sigma\) and what its output logic \(\omega\)? Since the multiplexer output drives both output \(Y\) and the next state input of the D-flipflop, the circuit in Figure 6.8 does not have the structure of the Mealy machine in Figure 6.23. Nevertheless, duplicating the multiplexer, as shown in Figure 6.25, reveals that the multiplexer loop is an optimized version of a vanilla Mealy machine that reuses the next state logic as output logic or vice versa.

Figure 6.25: Multiplexer loop of Figure 6.8 (left) with duplicated multiplexer to match the Mealy machine model of Figure 6.23 (right).

As another example, consider the shift register in Figure 6.13. The outputs \(Y_0,\) \(Y_1,\) \(Y_2,\) and \(Y_3 = S_{out}\) are driven by the registers. Therefore, the outputs are a function of the current state but not a function of input \(S_{in}.\) We conclude that the circuit is a Moore machine. The topology of the circuit in Figure 6.13 is simpler than that of the equivalent vanilla Moore machine in Figure 6.26, where the next state logic \(\sigma\) and output logic \(\omega\) are identity functions.

Figure 6.26: Shift register of Figure 6.13 (left) and with alternative topology of a Moore machine, see Figure 6.24 (right).

Since Mealy and Moore machines differ in their output behavior only, we can often use either type to solve a given problem. However, if we wish to generate the output within the cycle of a particular state and input, then a Mealy machine is required. A Moore machine cannot change the output while in the particular state. Instead, in a Moore machine we must wait until the next triggering clock edge, where the machine assumes the next state as a function of the particular state and input, and can then produce the desired output. On the other hand, a Moore machine has a more robust timing behavior, because the consumer of the output can rely on the fact that the output is stable during the entire cloci cycle after the propagation delay of the output logic has elapsed follwing the triggering clock edge. This delay is independent of changes of the input of the machine.

Machine Transformations¶

Occasionally FSM designers perceive a Moore machine as more natural than a Mealy machine. If a particular type of machine is desired, such perceptions can be overcome because we may translate one machine type systematically into the other. Figure 6.27 shows the two graphical rules for translating state \(A\) from a Mealy type into a Moore type state transition diagram and vice versa. Recall that we associate the output in a Mealy diagram with the input and in a Moore machine with the state.

Figure 6.27: Rules for transforming a Mealy state diagram into a Moore state diagram and vice versa.

Rule 1 states that state \(A\) in Mealy machine can be translated into an equivalent state \(A\) in a Moore machine if all incoming transitions of the Mealy machine have the same output. In this case, we associate the output with state \(A\) of the Moore machine. Conversely, we translate state \(A\) of a Moore machine into a Mealy machine by associating output \(O\) of the Moore machine with all inputs in the Mealy machine. Rule 2 covers the case where the incoming arcs of state \(A\) in the Mealy machine have different outputs. In this case, we replicate Mealy state \(A\) in the Moore machine for each distinct output. Conversely, we transform the Moore machine into a Mealy machine by merging Moore states \(A_1\) and \(A_2\) into Mealy state \(A,\) and by associating the outputs of the Moore states with the inputs of the Mealy transitions.

Rule 2 is the reason why, in general, Mealy machines require fewer states than Moore machines to solve a given problem. Hence, a Mealy machine may be constructed with fewer D-flipflops than the equivalent Moore machine. Whether the reduction in state bits leads to an overall savings in logic, including the next state and output logic, depends on the particular implementation, and requires a direct comparison of alternative designs.

6.3.2. Synthesis of Finite State Machines¶

The FSM designer uses the tools for the analysis of synchronous circuits, in particular the state transition diagram and the state transition table, to specify a FSM for a given problem description, and to implement the FSM as a synchronous sequential circuit. FSM synthesis may be viewed as reversal of the analysis procedure. Although synthesis requires more creativity than analysis, the synthesis of FSMs is a relatively systematic process.

The design methodology for an FSM can be summarized as a 6-step recipe:

- Identify inputs and outputs.

- Design a state transition diagram.

- Select a state encoding.

- Derive the state transition table.

- Minimize the next state and output logic.

- Synthesize the circuit.

Most of a designer’s creativity flows into step 2, where a problem description, typically provided as an informal statement, is formalized by means of a state transition diagram either of Mealy type or of Moore type. The other five steps are comparatively straightforward applications of established techniques.

Before we illustrate the FSM design methodology by means of several examples, let us clarify the role of the state register as the central element of every FSM. The state register holds the current state \(S,\) which we may observe at its output \(Q.\) State \(S\) remains stable for the entire clock cycle between triggering clock edges. Next state \(S'\) is stored at the next triggering clock edge. The next state logic computes \(S'\) as a function of the inputs \(I\) and current state \(S.\) Next state \(S'\) must be stable before the next triggering clock edge so that the state register can store the next state reliably. In Moore machines, the state register decouples the outputs from the inputs. Since the outputs are a function of current state \(S\) only, the inputs affect the outputs of the next state indirectly. In contrast, in a Mealy machine, the inputs bypass the state register so that the outputs react to changes at the inputs within the current clock cycle.

Serial Adder¶

We wish to design a serial version of a ripple carry adder. Assume that the binary summands appear one bit per clock cycle at inputs \(A\) and \(B,\) least significant bits first. The adder shall output the sum bits one per clock cycle, lsb first.

Following the design recipe, we find that step 1 is trivial whereas step 2 requires some thought. Recall that bit position \(i\) might generate a carry into position \(i+1.\) Since the summands appear at the inputs lsb first, imagine the lsb‘s appear in cycle 0, the bits of next position 1 in cycle 1, and so on. Thus, the bits of the summands in position \(i\) are available in cycle \(i,\) and we need to make the carry out of position \(i\) available as carry input during cycle \(i+1.\) We conclude that we need a 1-bit register that stores the carry-out at the next triggering clock edge, which separates current cycle \(i\) and next cycle \(i+1\) in time. The output of the register is the carry-in during cycle \(i+1.\) Since bit position \(i\) generates a carry or not, a 1-bit register suffices to distinguish these two states. Therefore, we decide to design the FSM with a 1-bit state register. Furthermore, we decide to design a Mealy machine.

We develop the state transition diagram of the Mealy machine, starting with two state vertices for state S0, meaning the carry-in is 0, and state S1 to represent a carry-in equal to 1 during the current clock cycle. Figure 6.28(a) shows the two state vertices. Next, we consider the state transitions. Since the current state represents the carry-in, the next state represents the carry out. Thus, our next state logic must implement the carry-out function of a full adder. The carry-out, i.e. the next state, is a combinational function that depends on the two inputs \(A\) and \(B\) and the carry-in, i.e. the current state \(S.\)

Recall that the carry-out of a full adder is 1 if two or three inputs are 1, and otherwise the carry-out is 0. First, we consider the outgoing transitions of state S0, see Figure 6.28(b). The only input combination that can generate a carry-out of 1 is \(A = B = 1.\) We draw an arc from S0 to S1, and annotate it with input combination \((A,B)=11.\) The remaining three input combinations do not generate a carry out. Therefore, we draw a looping arc at state S0, and annotate it with the three remaining input combinations. The outgoing transitions of state S1 are shown in Figure 6.28(c). With a carry-in equal to 1, the only input combination that causes the carry-out to be 0 is \(A = B = 0.\) We draw an arc from S1 to S0 for input combination \((A,B) = 00.\) The other three input combinations cause a carry-out of 1, represented by the loop pointing from S1 to S1. In Figure 6.28(d), we add the outputs to each input combination. The output of the serial adder is the sum bit. If the carry-in is 0, i.e. in state S0, the sum is 1 if exactly one of the inputs \(A\) or \(B\) is 1, otherwise the sum is 0. In state S1, representing a carry-in of 1, the sum is 1 if inputs \(A\) and \(B\) are equal. We also mark state S0 with another circle, indicating that S0 is the start state of the Mealy machine, because initially the carry into lsb position 0 should be 0.

Step 3 of the FSM recipe requires selecting a state encoding. We choose the natural encoding suggested by our design, \(S0 = 0\) and \(S1 = 1,\) because the state register should store the value of the carry. Using the opposite encoding is possible, but would be rather confusing. Next, we derive the state transition table according to step 4 of the FSM recipe. It shouldn’t come as a surprise that converting the state transition diagram of Figure 6.28(d) into a state transition table yields the truth table for the carry-out of a full adder, where the current state is the carry-in:

state A B next state Sum 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1

We have included the Sum output of the serial adder in the state transition table, because it adds just one more column to the truth table. Since the output of a Mealy machine is a function of the current state and the inputs, needed for the next state as well, this is faster and less error-prone than compiling a separate truth table for the output function. Note that the translation of the state transition diagram into the state transition table is a straightforward transliteration of the directed graph into truth table format. No knowledge specific to the purpose of our adder design is required, except the state encoding.

Step 5 of the FSM recipe asks us to minimize the next state and output logic. To that end, we apply the techniques developed for combinational logic design, for example K-maps. The K-maps for the next state \(S'\) and the Sum output

yield the well-known SOP expressions of the majority and odd-parity functions

Without further logic optimizations or technology mapping, we complete step 6 of the FSM recipe, and synthesize a circuit diagram for the serial adder using two-level combinational logic. Figure 6.29 shows the resulting Mealy machine in the topological form of Figure 6.23. The next state logic \(\sigma\) is the majority function and output logic \(\omega\) is a 3-variable XOR function.

Figure 6.29 completes the FSM design of the serial adder. Note that the serial adder consists of the combinational logic of one full adder plus one register. Compared to a ripple carry adder, which requires \(n\) full adders to add two \(n\)-bit summands, our serial adder FSM requires only one full adder, independent of \(n.\) However, our serial adder FSM requires \(n\) clock cycles to produce all sum bits. This is a typical example for the trade-off between space and time in digital logic.

Now that we have a Mealy machine, we have two options to design a Moore machine for the serial adder. Option 1 is to start from scratch, working ourselves through the six steps of the FSM recipe. However, step 2 of the recipe requires more creativity for a Moore machine than for the Mealy machine. This becomes clear after working through Option 2, deriving the Moore machine from the Mealy machine using machine transformations. The state transition diagram of the Mealy machine in Figure 6.28(d) shows four incoming transitions for each state with different outputs, 0 or 1. Therefore, we apply Rule 2 and split each Mealy state into two Moore states, as shown in Figure 6.30. Moore state \(S0_0\) represents a carry-in of 0 with sum output 0 and Moore state \(S0_1\) represents a carry-in of 0 with sum output 1. Analogously, Moore states \(S1_0\) and \(S1_1\) represent a carry-in of 1 with the corresponding outputs.

The state transition diagram of the Moore machine in Figure 6.30 is significantly more complex than the corresponding diagram of the Mealy machine. This is, of course, why we present the design of the Mealy machine for the serial adder to begin with. We leave it as an exercise to complete the design of the Moore FSM.

Pattern Recognizer¶

We receive a periodic binary signal and wish to recognize patterns of two consecutive 1’s. To solve this problem, we follow the FSM design recipe.

At the first glance, the problem description appears to be rather vague. However, step 1 of the recipe gives us a chance to tie up loose ends by defining the inputs and outputs of our pattern recognizer machine. The binary signal constitutes a 1-bit input; call it \(A.\) Since the binary signal is periodic, we assume a clock signal \(\phi\) with the period of input \(A.\) To indicate recognition of two consecutive 1’s in input \(A,\) we attach a 1-bit output, say \(Y,\) to the machine. Our goal is to set output \(Y\) to 1 after recognizing two consecutive 1’s in \(A\) and to 0 otherwise. The block diagram on the right summarizes our findings.

Following step 2 of the design recipe, we model the problem as a state transition diagram. With little information in the problem description to go on, our best bet is to examine the sampling behavior of the input signal with a concrete example. As shown in Figure 6.31, we assume that clock \(\phi\) and input \(A\) have the same period. Furthermore, to facilitate reliable sampling, input signal \(A\) must be stable before and at the positive clock edge. As shown in the waveform diagram, we assume that signal \(A\) changes shortly after the positive clock edge. Thus, \(A\) is stable during most of the clock cycle and, in particular, at the triggering clock edge at the end of the cycle. This timing behavior gives our machine enough slack to compute the next state during the clock cycle, and store the next state at the end of the cycle. Under these assumptions, we count time in the waveform diagram in multiples of clock cycles.

To simplify the problem even further, we ignore the details of the timing behavior, and use abstract binary sequences for the input and output signals of the machine. The input sequence in Figure 6.31 is

In the following, we refer to element \(i\) of sequence \(A\) as \(A[i],\) and interpret \(A[i]\) as the Boolean value of input signal \(A\) during cycle \(i.\) For example, \(A[0] = 0\) and \(A[2] = 1.\)

Next, we develop the desired output signal for input sequence \(A.\) Assume output \(Y\) is initially 0, until we have seen the first pair of inputs \(A[0] = 0\) in cycle 0 and \(A[1] = 0\) in cycle 1. Since two consecutive 0’s differ from the 11-pattern we are looking for, we set the output to 0. Since we need to inspect the inputs during cycles 0 and 1, it seems natural to assign 0 to output \(Y\) during cycle 2 after receiving two input bits. Thus, we pursue a timing behavior where the machine inspects the first input bit \(A[t]\) during cycle \(t,\) the second input bit \(A[t+1]\) during cycle \(t+1,\) and asserts the corresponding output \(Y[t+2]\) during cycle \(t+2.\) In Figure 6.31, the first pair of consecutive 1’s is \(A[2]=1\) and \(A[3]=1,\) so that cycle 4 is the first cycle where we set \(Y[4]=1.\) During cycle 5 we set \(Y[5]=0,\) because \(A[3] =1\) and \(A[4]=0.\) The second pair of consecutive 1’s appears in cycles 8 and 9, \(A[8]=1\) and \(A[9]=1.\) Therefore, we set \(Y[10]=1.\) Cycle 9 presents a notable case, because \(A[9]=1\) and \(A[10]=1.\) Hence, we set \(Y[11]=1.\) This case is notable, because input \(A[9]=1\) belongs to two overlapping pairs of 11-patterns. We interpret our problem description to recognize 11-patterns as recognizing every 11-pattern, and include overlapping patterns. As a result our pattern recognizer should produce the output sequence

for input sequence \(A.\)

The sequence abstraction is crucial for the design of a finite state machine. First, however, we have to decide on the type of the machine, Mealy or Moore machine. Our earlier decision to assign the output during the cycle after inspecting two consecutive input bits implies a Moore machine. The waveform diagram in Figure 6.31 clarifies this implication. Consider cycle 4, where output \(Y[4]=1\) in response to recognizing 11-pattern \(A[2] = A[3] = 1.\) Output \(Y\) should be independent of input \(A,\) or \(Y\) might switch to 0 during cycle 4 when \(A\) switches from 1 to 0. In a Moore machine, output \(Y\) is independent of the input and, therefore, switches at the triggering clock edges only, as indicated by the arrows in Figure 6.31.

We are ready to design the state transition diagram for a Moore type pattern recognizer. Since the number of required states is not immediately obvious, we develop the states incrementally. We begin with start state S0, where we wait for the first 1 to appear in input \(A.\) When the first 1 occurs, we transition to a new state S1. Otherwise, we stay in state S0 and output \(Y=0.\) Figure 6.32(a) shows start state S0 and its two outgoing transitions. Next, consider state S1. We transition into S1 after observing one 1 on input \(A.\) Since we have not observed two 1’s, we output \(Y=0.\) If we observe input 0 while in S1, we return to S0, and wait for the next 1 to appear. Otherwise, if we observe input 1, we transition to new state S2, see Figure 6.32(b). In state S2, we have received two consecutive 1’s in the two preceding cycles. Therefore, we output \(Y=1.\) The transitions out of state S2 are shown in Figure 6.32(c). If we observe input 1, we encounter the case of overlapping 11-patterns. We remain in state S2 and output \(Y=1.\) Otherwise, if input \(A=0,\) we return to state S0 and wait for the next 1 to appear in the input. This completes the state transition diagram.

We continue with step 3 of the design recipe, and select a state encoding. The Moore machine in Figure 6.32(c) has three states. Thus, we need at least \(\lceil \lg 3\rceil = 2\) bits to encode three states. We choose a binary encoding of the state number:

state binary encoding S0 00 S1 01 S2 10

The binary encoding seems natural, but is not necessarily the best choice. Other choices may reduce the cost of the next state and output logic. However, the binary state representation minimizes the width of the state register. For our Moore machine, we need a 2-bit state register with binary state \(S = S_1 S_0.\)

Given the state encoding, we can develop the state transition table according to step 4 of the design recipe. The table defines the state \(S' = S_1' S_0'\) as a function of the current state \(S = S_1 S_0\) and input \(A.\) For clarity, we also include columns for the corresponding state names used in the state transition diagram of Figure 6.32(c).

\(S\) \(S_1\) \(S_0\) \(A\) \(S'\) \(S_1'\) \(S_0'\) S0 0 0 0 S0 0 0 S0 0 0 1 S1 0 1 S1 0 1 0 S0 0 0 S1 0 1 1 S2 1 0 S2 1 0 0 S0 0 0 S2 1 0 1 S2 1 0

The state transition table is a truth table that specifies the combinational next state logic. More succinctly, the next state logic is a multioutput function \(S' = \sigma(S, A)\) where \(S_1'\) and \(S_0'\) are Boolean functions in three variables, \(S_1,\) \(S_0,\) and \(A.\)

Furthermore, we compile a truth table for the output logic. Output \(Y\) of the Moore machine is a function of the current state \(S = S_1 S_0.\) The state transition diagram in Figure 6.32(c), specifies in each state vertex the associated output, which we summarize in a separate truth table.

\(S\) \(S_1\) \(S_0\) \(Y\) S0 0 0 0 S1 0 1 0 S2 1 0 1

Following step 5 of the design recipe, we minimize the next state and output logic. We use K-maps for the incompletely specified functions

to derive the minimal SOP expressions

Last but not least, we obtain the circuit diagram in Figure 6.33, which realizes step 6 of the design recipe. The output logic is the trivial identity function. To enter start state S0, we assume that the register has a separate reset input that enables us to reset all D-flipflops.

Now that we have a complete design for the pattern recognizer as a Moore machine, we amortize our intellectual investment by designing a Mealy machine for direct comparison. We restart the design process at step 2 of the recipe. Figure 6.34 shows the waveform diagram with the same input signal as in Figure 6.31, assuming that output \(Y\) depends not only on the state but also on input \(A.\) We exploit the combinational dependence on input \(A\) to redefine the timing behavior of output \(Y,\) such that \(Y=1\) during the clock cycle when the second 1 appears on input \(A.\) More precisely, if \(A[t] = 1\) during cycle \(t\) and \(A[t+1] = 1\) during cycle \(t+1,\) then we can set \(Y[t+1]=1\) in a Mealy machine, which is one cycle earlier than in the Moore machine.

Consider the first occurance of two consecutive 1’s in cycles 2 and 3. The Mealy machine sets output \(Y\) to 1 during cycle 3 already. Note that output \(Y\) will remain 1 at the beginning of cycle 4 until \(A\) changes from 1 to 0. Indeed, the timing behavior of output \(Y\) of the Mealy machine is not as clean as that of the Moore machine. The output may even exhibit glitches as at the beginning of cycle 6. However, if we sample output \(Y\) toward the end of the cycle, then the behavior is as expected: we observe \(Y=1\) at the positive clock edges at the end of cycle 3, cycle 9, and cycle 10.

The state transition diagram of the Mealy machine requires only two states. State S0 is the start state, which waits for the first 1 to appear on input \(A.\) When \(A=1,\) we transition to state S1, and output \(Y=0.\) If \(A=1\) in state S1, the 1 input must have been preceded by another 1, so we output \(Y=1\) and remain in state S1. If input \(A = 0\) in state S0 or S1, the machine outputs \(Y=0\) and transitions to next state S0. The Mealy machine saves one state compared to the Moore machine.

The remaining steps of the design recipe involve straightforward design work. Since the Mealy machine has two states, we need a 1-bit register to store \(S=0\) representing state S0 and \(S=1\) for state S1. We translate the state transition diagram in Figure 6.35 into the combined truth table for the next state logic and output logic:

\(S\) \(A\) \(S'\) \(Y\) 0 0 0 0 0 1 1 0 1 0 0 0 1 1 1 1

We can spot the minimal Boolean expressions in the truth table without the aid of K-maps: next state \(S' = A\) and output \(Y = A \cdot S.\) The resulting circuit diagram of the Mealy machine is shown in Figure 6.36. The machine is a degenerate Mealy machine without a feedback loop.

Comparison with the Moore machine in Figure 6.33 shows that the Mealy machine needs one D-flipflop rather than two and only one gate rather than four. These hardware savings come at the expense of a noisy timing behavior. If the clean timing behavior of the Moore machine output is desired, we can have it albeit at increased hardware cost.

Traffic Light¶

Perhaps the seminal application of finite state machines is the traffic light controller. The animation in Figure 6.37 shows the baroque Austrian style, which ends the green phase in a flashy trill.

Figure 6.37: Austrian traffic light animation.

Designing a controller FSM for the traffic light requires determining a suitable clock period. A simple, natural choice is the shortest duration that any light is switched on or off. Assume that the blinking green light at the end of the green phase determines the clock period \(T,\) and all other phases last a multiple of \(T\):

phase duration red \(13\,T\) red-yellow \(4\,T\) green \(5\,T\) green blinking \(1\,T \times 4\) yellow \(4\,T\)

Given this problem description, we design an Austrian traffic light controller follwing the FSM recipe. First, step 1, we define the inputs and outputs. Other than the clock signal, our rudimentary controller receives no data inputs. Standard traffic lights consist of three colored lights, red, yellow, and green. The controller switches each of the three lights on or off. Therefore, we attach three 1-bit outputs, \(R,\) \(Y,\) and \(G.\) If the output is 1, the associated light shall be switched on and otherwise off.