1. Electrical Foundations¶

Digital circuits are a special class of electrical circuits that operate with discrete values of voltages. In today’s digital systems, we use two voltages to represent discrete values, high and low voltage. The specific voltage values are of secondary importance, and vary across different implementations and technologies. Of course, most of us have experienced voltage as a phenomenon of the macroscopic, continuous world, where switching between high and low voltages is not an instantaneous event but a continuous process that takes time to transition through intermediate voltages. If the time to switch between voltages is irrelevant compared to the time the system rests at a particular voltage, we may consider the two relevant states of high and low voltage only, and disregard the intermediate voltages during the transition. This focus on the essential property of interest, the steady voltages rather than the transition between them, is part of the digital abstraction.

The digital abstraction is the basis of digital logic. An important application of digital logic is to argue about the correctness of programs, where we care about sequences of discrete states. To keep such arguments comprehensible, we ignore the details of how the transition between states occurs at the voltage level. However, the speed of the transition is the crucial property that determines the performance of a computation. Since electrical processes are blazingly fast, and can be controlled in a highly reliable and reproducible fashion, we build today’s computers with electrical circuits, digital circuits to be precise. Speed is an important property of digital circuits, not only because faster circuits enable faster computers, but also because faster circuits consume more power than slow circuits. For example, when targeting low-power computers for cell phones, we may trade speed for reduced power consumption. Thus, knowing how to design fast versus slow digital circuits is essential for computer engineers, just like the techniques to build a Porsche differ from those for a Trabi. This chapter recaps the electrical foundations of digital circuits, as far as we need them to understand both their logical functionality and speed.

1.1. Current, Voltage, and Energy¶

We begin with a review of the basic concepts that enable us to understand the phenomena associated with electricity: charge, current, voltage, energy, and power.

(1736-1806)

Electrical charge is a fundamental property of matter. Regular mortals can neither create nor destroy electrical charge. Consequently, in our circuits charge is conserved by nature. An electron has the smallest unit of charge that exists, the negated elementary charge

and a positron has a positive elementary charge \(q.\)

Unit \(C\) honors the French physicist Coulomb, who formulated the law that describes the electrostatic force between two charges \(q_1\) and \(q_2\)

where constant \(k = 8.99 \times 10^9\,N m^2 / C^2\) and \(d\) is the distance between the charges. Force \(F\) is attractive, if the charges have opposite signs, otherwise \(F\) is repulsive. We can imagine the force as a vector field. In free space, the field emanates radially from an electrical charge. The direction of the field gives the direction of the force on a positive test charge. In Figure 1.1, the field lines of an electron point toward the electron, indicating that the electron attracts a positive test charge, whereas the field lines of the positron point outwards, because a positron repells a positive test charge.

An electron experiences the force field of a charge at distance \(d=1 mm\) (milli-meter). The force of \(F = 9.81 mN\) (milli-Newton) attracts the electron. This is the force mother Earth’s gravity exerts on a mass weighing \(1 g\) (gram). How big and of which type is the charge?

Answer: The charge must be positive, because it attracts the electron. If the electron has charge \(q_1 = -1.602 \times 10^{-19} C,\) the charge at distance \(d\) is

which is the charge of approximately \(4.25 \times 10^{19} (\approx q_2 / q)\) positrons. In this calculation, we presume that an attractive force is negative, so that the minus signs of the force and electron charge cancel each other out, and \(q_2\) is positive.

(1775–1836)

An electrical current is charge in motion. Quantitatively, current \(i\) is a rate, the number of charges moved through an area per unit of time. The area may be the cross section of a wire, for example. In general, current \(i(t) = dq / dt\) changes instantaneously over time \(t,\) i.e. the current is the derivative of \(q\) with respect to \(t.\) We refer to the average current \(I = \Delta q / \Delta t\) over finite time period \(\Delta t\) with an upper case letter \(I.\) The unit for current is the Ampere, \(1 A = 1 C/s,\) in honor of the French physicist Ampère.

A cell phone battery is rated to produce \(1 A h\) (amp \(\cdot\) hour). How long does the battery last if the phone draws an average current of \(100 mA\)?

Answer: Battery ratings state the capacity or, more precisely, the total charge \(Q\) the battery can produce. Rather than using Coulombs, battery manufacturers prefer the unit amp-hour. Since one hour has 3600 seconds, \(1 A h = 3600 A s = 3600 C.\) If we discharge the battery at a rate of \(1 A,\) i.e. we consume current \(I = 1 A\) on average, the battery lasts for one hour. If the average current is only \(I = 100 mA,\) we can draw this current for a longer time period of time:

This straightforward calculation surely confirms your intuition: your phone will last longer if you talk less or plug in a battery with larger capacity.

Electrical charges flow through wires pretty much like water flows through pipes. Therefore, we sometimes use fluids as an aid for imagining how electrical currents flow through circuits, including practically useful circuits with producer and consumer devices. Figure 1.2 contrasts circuits built from pipes and wires.

Figure 1.2: On the left, a fluid flow is produced by a pump and energy is consumed by a turbine. On the right, an electrical current is produced by a battery and energy is consumed by a light bulb.

Consider the closed water loop on the left of Figure 1.2 that connects a pump and a turbine. The pump generates a flow of water, which is used to rotate the turbine. In such a system, the flow \(U\) of water atoms per time unit is the same everywhere in the loop, and in particular before and after the turbine. However, the water pressure \(P_H\) before the turbine is higher than water pressure \(P_L\) after the turbine. The pressure difference represents the energy that the turbine transforms into rotations. The analogon to the water loop is the electrical circuit shown on the right in Figure 1.2. The battery generates an electrical current that causes the bulb to light up. The current \(I\) is the same before and after the light bulb. Analogous to the water pressure, voltage \(V_H\) before the light bulb is higher than voltage \(V_L\) after the bulb. The voltage difference represents the energy that the light bulb transforms into light and heat.

(1818-1889)

Electrical energy represents the effort required to move an electrical charge through an electrical field, for example inside a wire or a device. We use symbol \(w\) to denote energy, and the unit Joule (\(J\)) in honor of the English physicist Joule.

(1745-1827)

Voltage measures the energy (in Joule) to move a positive unit of charge (1 Coulomb) against the force of an electrical field. We use symbol \(v\) for voltage, and unit Volt, \(1 V = 1 J / C,\) in honor of the Italian physicist Volta. Formally, voltage is defined as the derivative \(v = d w / d q.\) Constant or average voltage is denoted with upper case \(V.\)[1]

The voltage difference across the light bulb in Figure 1.2 is \(V = V_H - V_L.\) This is the voltage the battery exerts on the bulb. If the light bulb transforms \(100 J\) of electrical energy in \(1 s\) into light and heat, and the battery generates voltage \(V = 230 V,\) what is the current through the circuit and how much charge does the battery move through the bulb in \(1 h\)?

Answer: At a voltage of \(230 V\) the lightbulb requires

of charge to move through within \(1 s.\) Thus, the current through the circuit is \(I = \Delta q/\Delta t = 435 mA.\) To provide light for \(T = 1 h = 3600 s,\) the battery has to supply a total charge of \(Q = I \cdot T = 435 mA h,\) or in Coulomb \(Q = 0.435 A \cdot 3600 s = 1565.2 C.\)

(1736-1819)

Electrical power is the rate at which electrical energy is consumed per time unit (or produced by a power source):

We use the symbol \(p\) for power, and the unit Watt, \(1 W = 1 J / s = 1 V A,\) in honor of the Scottish engineer Watt. The average power \(P = \Delta w/\Delta t = V \cdot I\) is the average energy consumed per unit of time.

Electrical appliances like microwave ovens or light bulbs are commonly characterized by their power consumption, e.g. a \(10 W\) light bulb or a \(900 W\) microwave. In contrast, the monthly electricity bill for your household is commonly based on the price for energy, e.g. 8 Cent per \(kWh\) (kilo-Watt-hour). How much do you need to pay for electricity if you use the microwave for \(2 h\) and the light bulb for \(150 h\)?

Answer: Power denotes the energy consumption per time unit. The total energy consumed is determined by the duration for which we use an appliance. Thus, energy is the quantity it’s worth paying for, not power. If the microwave consumes a power of \(900 W,\) then using the microwave for 2 hours consumes an energy of \(900 W \cdot 2 h = 1.8 kWh,\) or in Joule \(900 W \cdot 7200 s = 6480 kJ,\) because \(1 J = 1 W s.\) Analogously, your energy consumption for lighting is \(10 W \cdot 150 h = 1.5 kWh.\) Thus, the monthly electricity bill costs you \((1.8 + 1.5) kWh \cdot 8\) Cent\(/ kWh = 26.4\) Cent.

Determine the electrostatic force between an electron and a proton in a hydrogen atom, assuming that a proton carries a positive elementary charge and the distance between the particles is \(0.53 \times 10^{-10} m.\) What is the mass of a body on the surface of the Earth that experiences the equivalent gravitational force, assuming that the mass of planet Earth is \(5.976 \times 10^{24} kg\) and its radius is \(6378 km\)?

An electron carries a negative elementary charge \(q_e = - 1.602 \times 10^{-19} C\) and the proton positive elementary charge \(q_p = 1.602 \times 10^{-19} C.\) At the given distance of \(d = 0.53 \times 10^{-10} m\) within the hydrogen atom, the electrostatic force between the particles is:

The minus sign indicates that the electrostatic force attracts the particles toward each other.

Newton’s law of gravitation states that the attractive gravitational force between two masses \(m_1\) and \(m_2\) and their centers of mass separated by distance \(r\) is:

where \(G = 6.67 \times 10^{-11} m^3/ (kg\,s^2)\) is the gravitational constant. To determine the mass of a body \(m_b\) on the surface of planet Earth such that the gravitational force equals the electrostatic force within a hydrogen atom, we equate the absolute value of \(F_e\) and \(F_g,\) and solve for \(m_b\):

Given that an electron has a mass of \(9.11 \times 10^{-31} kg,\) body mass \(m_b\) is huge and the mass of planet Earth is humongous. Even though \(r_{Earth} \gg d,\) this comparison indicates that the electrostatic force is significantly stronger than the gravitational force.

If you need a replacement for your rechargeable cell phone battery, you find that battery manufacturers advertise the capacity of their products with different specifications. Show that the rating for a Lithium-Ion battery of \(10.78 Wh\) at \(3.85 V\) is equivalent to the rating of \(2800 mAh.\)

The rating of \(2800 mAh\) specifies an electrical charge, because the unit mAh indicates a product of current and time. Since \(1 mAh = 0.001 A \times 3600 s = 3.6 C,\) the rating tells us that the Lithium-Ion battery is capable of storing a charge of \(3.6 C.\)

In contrast, the rating of \(10.78 Wh\) at \(3.85 V\) specifies the amount of energy that the battery can store. The unit \(Wh\) indicates the product of power and time. Since \(1 Wh = 3600 Ws = 3.6 kJ,\) the rating \(10.78 Wh\) specifies an energy of \(10.78 \times 3.6 kJ = 38.8 kJ.\) The additional information that the battery has a voltage of \(3.85 V\) enables us to deduce the charge it can store. To that end we use the units as a guide, and notice that a charge of \(1 C = 1 A s = 1 Ws / V\) because \(1 W = 1 V A.\) Thus, we find that charge \(Q\) in Coulomb is equal to energy \(E\) in Joule, \(1 J = 1 Ws,\) divided by voltage \(V\) in Volt \(V\):

Since the battery rating specifies energy \(E\) in \(Wh\) and charge \(Q\) in \(mAh,\) we introduce a conversion factor of 1000 to compensate for the milli-prefix of the amps:

Using this formula, we can verify that the battery rating \(Q = 2800 mAh\) is indeed equivalent to the rating \(E = 10.78 Wh\) at \(V = 3.85 V,\) because \(1000 \times (10.78 / 3.85) = 2800.\) The latter rating provides you with the important information that your replacement battery must supply a voltage of \(3.85 V,\) though.

Tesla’s Model S electric car is rated to cover 306 miles at a constant speed of \(55 mph\) (miles-per-hour). The battery pack is capable of storing \(85 kWh,\) and consists of 7104 small Lithium-Ion cells organized in groups of 74 cells connected in parallel and 96 groups connected in series. Assuming that each cell generates \(3.8 V,\) determine the current the battery pack supplies to the electric motor when exhausting the advertised range of 306 miles at a speed of \(55 mph\) and the electrical charge stored in each cell.

The time it takes to cover a range of 306 miles at a constant speed of \(55 mph\) is:

The power consumption during this trip is the average energy supplied by the battery pack over time period \(T\):

The electrical current supplied by the battery pack to the electrical motor of the vehicle is \(I = P / V.\) To determine the voltage of the battery pack, we need to examine the organization of the Lithium-Ion cells within the pack. We note that composing battery cells in series enables us to increase the total voltage whereas composing cells in parallel increases the total current the composition can supply, illustrated in the Figure below. Furthermore, the total energy stored in a composition is the sum of the energies stored in each cell, independent of whether the cells are composed in series or in parallel.

Figure [Series and Parallel Battery Compositions]: On the left, two battery cells are composed in series by connecting the positive terminal of one cell with the negative terminal of the other cell. The total voltage of the composition is the sum of the cell voltages. On the right, two battery cells are composed in parallel by connecting the positive terminals and the negative terminals, respectively. The total voltage of the composition equals that of each cell, but the composition can supply twice the current as a single cell.

Each group of Tesla’s battery pack consists of 74 cells composed in parallel. The total voltage of a group is hence equal to the voltage of a single cell given as \(V_{cell} = 3.8 V.\) The pack is a series composition of 96 groups with a total voltage of

We conclude that the current supplied by the battery pack for \(5.56 h\) driving at a speed of \(55 mph\) is

The total energy of the battery pack is given as \(E_{pack} = 85 kWh.\) Since the total energy is the sum of the energy stored in each of the 7104 cells, the energy capacity of a cell is

This is the energy of a battery cell at voltage \(V_{cell} = 3.8 V.\) Therefore, the electrical charge stored in each cell must be according to Exercise 1.2

Rechargeable Lithium-Ion cells with this capacity are among the most commonly used today. They do not only power electric vehicals but also cell phones, laptops, and many other electronic devices.

1.2. Ohm’s Law¶

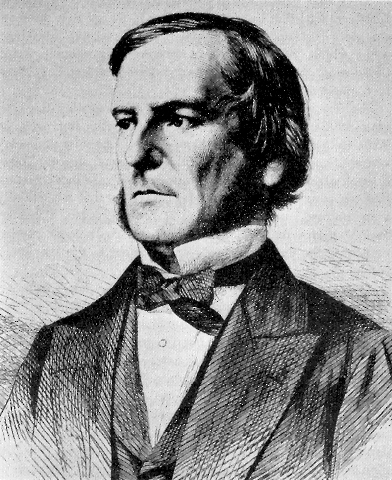

(1789-1854)

A resistor is an electrical device with resistance \(R.\) The unit of resistance is the Ohm, abbreviated with a Greek Omega, \(1 \Omega = 1 V / A,\) in honor of the German physicist Ohm.

Figure 1.3: On the left, fluid flow \(U\) is determined by the smallest cross section of the pipe. On the right, electrical current \(I\) is determined by the resistor.

Figure 1.3 illustrates the analogon between fluid flow through a pipe and electrical current through a wire with a resistor. By conservation of water in a pipe, the same amount of water must flow per time unit through any cross section of the pipe. Therefore, we can restrict the total flow by reducing the cross section at one point in the pipe. Analogously, we can reduce the current flowing through a wire by inserting a resistor.

Ohm discovered that the voltage across a resistor is proportional to the current flowing through it, and identified the resistance as the proportionality constant. This linear relationship between voltage and current is known today as Ohm’s law, and is the reason why unit \(\Omega\) is defined as \(1 \Omega = 1 V / A.\)

Ohm’s law

The voltage across a resistor is proportional to the current flowing through it:

Use upper-case letters to indicate time independent currents and voltages: \(V = R \cdot I.\)

Ohm’s law looks simpler than it is. Recall that voltage forces charges to move in a particular direction, and we have positive and negative charges, that we represent as positive and negative quantities. Ohm’s law assumes conventions about the direction of the voltage and current of the resistor to be applied as intended. The first convention is the sign convention for currents flowing through a wire or two-terminal device like a resistor. A current in the direction of positive charges shall be a positive current. In Figure 1.4, the arrow head indicates that current \(i\) flows top to bottom, i.e. positive charges flow downward. However, most technologies today move electrons, i.e. negative charges, through circuits rather than positive charges. We can produce a positive current either with positive charges moving in the indicated direction, or with negative charges flowing in the opposite direction, or both. Ohm’s law applies to any current, independent of the underlying physical mechanism.

The second convention involves the use of reference directions for voltages and currents in circuits. We use arrows to specify a reference direction of a current in a circuit. If the actual current flows in the opposite direction, we negate the current. In Figure 1.4, the arrow head specifies the reference direction of current \(i\) through the resistor. If, today the current flows is the reference direction, the current is positive \(i.\) If, tomorrow, we force a current in the opposite direction, the current is negative \(-i\) w.r.t. the reference direction. As the driving force behind a current, voltage is a directed quantity too. It is common practice to indicate voltages by polarity, using plus (\(+\)) signs and minus (\(-\)) signs: polarity \(+\) for high voltage and polarity \(-\) for low voltage. The plus and minus signs define the reference direction for the voltage from high to low. Alternatively, we use an arrow pointing from high to low voltage, as shown on the left in Figure 1.4. If, today, we connect the \(+\) terminal of a battery to the upper terminal of the resistor and the \(-\) terminal of the battery to the lower resistor terminal, the voltage across the resistor is positive. If, tomorrow, we swap the battery connections, the voltage at the lower resistor terminal is higher than at the upper resistor terminal, and the voltage across the resistor is negative w.r.t. the reference direction. You can think of reference directions as a generalization of the Cartesian coordinate system for arbitrary circuit topologies.

A resistor is not a power source like a battery. Therefore, voltage \(v\) across a resistor does not represent the force that drives current \(i\) through the resistor, but the voltage difference that current \(i\) induces at the resistor terminals. In essence, a resistor is a consumer that transforms electrical into thermal energy, similar to a light bulb. For example, if a battery forces current \(I = 10 A = 10 C/s\) through the resistor, and you measure a voltage difference of \(V = 2 V\) at its terminals, this means that the resistor dissipates \(2 V \cdot 10 C = 20 J\) of electrical energy during one second. The same information is available through resistance \(R = V / I = 0.2 \Omega\) due to Ohm’s law. Should you ever measure voltage \(V = -2 V\) at the resistor terminals, Ohm’s law tells you that the actual current is \(I = V / R = -10 A,\) i.e. it flows against the reference direction. Furthermore, the energy the resistor consumes in one second is \((-2 V) \cdot (-10 A) \cdot 1 s = 20 J,\) independent of the direction. You can avoid confusion and unnecessary minus signs in your calculations by choosing the reference directions for current and voltage at a resistor to be the same. In terms of the direction of the current flow, Ohm’s Law is the electrical version of the wisdom that water always flows downhill.

(1816-1892)

Occasionally, calculations with resistors tend to be more convenient when using the reciprocal of the resistance. The conductance of a resistor is the reciprocal of its resistance, \(G = 1 / R.\) The unit of conductance is the Siemens, \(1 S = 1 A / V,\) in honor of the German industrialist Siemens.

Electrical appliances like toasters use a constantan wire to convert electrical into thermal energy. Constantan wire has a high resistance that is essentially constant across a wide range of temperatures, hence its name. Assume that the constantan wire of your toaster has a resistance of \(46 \Omega.\) Determine the electrical current and power consumption when operating the toaster at a voltage of \(230 V.\)

According to Ohm’s law, the current through the constantan wire with resistance \(R = 46 \Omega\) is

Therefore, the power consumption of the toaster is

We can use Ohm’s law \(V = R I\) to derive equivalent expressions for the power consumption that can simplify the power calculation:

The third expression enables us to deduce the power consumption of the toaster given the voltage and resistance directly, without calculating the current first: \(P = V^2 / R = 230^2 / 46 W = 1150 W.\)

The resistance depends on the intrinsic resistivity \(\rho\) of a material and its geometric shape. Imagine that an ideal wire has the geometry of a long cylinder, whereas wires in integrated circuits assume the shape of a cuboid:

The resistance of both wires is \(R = \rho \frac{l}{A},\) where \(l\) is the length and \(A\) is the area of the cross section through which a current flows if we apply a voltage to the terminals. Copper, for instance, has a resistivity of \(\rho_{Cu} = 1.7 \times 10^{-8} \Omega m,\) whereas the resistivity of polycrystalline silicon on a chip can be tailored within range \(10^{-5} \Omega m \lesssim \rho_{poly} \lesssim 10^2 \Omega m.\) Determine the resistance of a copper wire with radius \(r = 1 mm\) and length \(l = 10 m,\) as well as the current and dissipated power if we apply a voltage of \(230 V.\) For comparison, determine the range of resistances of a polycrystalline silicon wire of height \(h = 20 nm,\) width \(w = 100 nm,\) and length \(l = 1 \mu m,\) as well as the current and dissipated power if we apply a voltage of \(1 V.\)

We consider the cylindrical copper wire first. The area of the cross section is the area of a circle with radius \(r\):

The resistance of the copper wire with a length of \(10 m\) is then

If we apply a voltage of \(230 V\) to the ends of the wire, the current is through the wire is determined by Ohm’s law \(V = R I\):

The wire consumes electrical power

and dissipates the power in form of heat. The copper wire of this example could be in a common household power cord, and gives you a glimpse on what might happen if you connect its ends to the terminals of your wall outlet. The projected massive power consumption could easily set your home on fire weren’t it for your circuit breaker to trip.

Next, we consider the polycrystalline silicon wire, or poly wire for short. The cross section of poly wires is approximately rectangular, considering how VLSI manufacturing processes deposit a thin layer of poly of constant height on the surface of a chip. The cross section area of the poly wire is

The resistance of the poly wire with \(1 \mu m\) length is

Given the range of poly resistivity, the resistance of the poly wire can be in range

Applying a voltage of \(1 V\) to the terminals of the poly wire, the current will be in range

and the consumed power

At the high end of the range the associated heat dissipation of \(200 \mu W\) with a wire resistance of \(5 k\Omega\) is likely to melt the chip over time. At the low end, the resistance of \(5 \times 10^{10} \Omega\) acts almost like an insulator, causing an uncritical heat dissipation of \(20 pW\) only.

The use of plus and minus signs to express electrical polarities is a great mathematical trick. It encodes in the sign of a number whether the actual voltage or current through an electrical device has the same or the opposite direction of an arbitrarily chosen reference direction. Furthermore, it enables us to determine algebraically whether a device produces or consumes electrical energy. Assume you excavate a cable section with two wires, and measure voltage \(V = 6 V\) and current \(I = -2 mA\):

Determine which of circuits A and B is the producer and which the consumer, and how much power the cable transfers from producer to consumer.

Let’s pretend that the excavation of the cable section does not reveal circuits A and B at its ends. Therefore, the directions chosen for the voltage and current measurements serve as arbitrary reference directions. Since voltage \(V = 6 V\) is positive, the actual voltage direction matches the reference direction. Thus, the voltage of the top wire is by \(6 V\) higher than the voltage of the bottom wire. In contrast, the negative current measurement of \(I = -2 mA\) tells us that the current of magnitude \(2 mA\) flows actually in the opposite direction from circuit B to circuit A through the top wire. We deduce that circuit B is a producer, for example a battery that supplies a voltage of \(6 V,\) and circuit A is a consumer, for example a resistor with resistance \(R = V / I = 3 k\Omega\):

We annotate the circuit to reflect the actual directions of voltage and current. The plus and minus signs signify the polarities of the terminals. As a result of this informed choice of directions, both voltage and current values are positive. This circuit diagram is consistent with Figure 1.4, because the directions of the current through and the voltage across the resistor are the same. We conclude that the power consumed by the resistor is \(P = V I = 6 V \cdot 2 mA = 12 mW.\) This is the same power that the batter produces. Thus, the cable transfers an energy of \(12 mJ\) per second from circuit B to circuit A. This insight assumes the so-called passive sign convention, which decrees that the power consumed by a passive device like a resistor is counted positive, whereas the power produced by an active device such as a battery is counted negative. In general, a current enters a consumer at the high voltage terminal, whereas a current exits the high voltage terminal of a producer. In case of our energy producing battery the current of \(2 mA\) exits its high voltage terminal. The current flows in the opposite direction through the battery as the voltage drops. To determine the power produced by the battery, we align the directions of voltage and current by negating the current. We find that the power consumption of circuit B is \(P = V \cdot (-I) = -12 mW,\) and interpret the negative power consumption as power production.

1.3. Kirchhoff’s Laws¶

Ohm’s discovery of the relationship between voltage and current marked the beginning of circuit theory, the abstract mathematical study of the properties of electrical circuits. Gustav Kirchhoff generalized Ohm’s law, and discovered two basic properties of electrical circuits that facilitate the analysis of nontrivial circuit topologies.

1.3.1. Kirchhoff’s Current Law¶

(1824-1887)

The first observation is concerned with the current flow across nodes, i.e. points in a circuit where multiple wires are connected. We invoke our pipe analogy again: If three water pipes are joined, the sum of the flow rates of the incoming water is equal to the flow rate of the outgoing water. Figure 1.5 illustrates the analogy for a joint of water pipes and a node of electrical wires.

Figure 1.5: What goes in must come out: the flow of water is conserved across pipe joints (left) and, likewise, the flow of electrical charges is conserved across wire joints (right).

Figure 1.5 suggests that outgoing current \(I_3\) is the sum of the incoming currents \(I_1\) and \(I_2,\) i.e. \(I_3 = I_1 + I_2.\) If this were not true, the node would either leak or inject charges, or the charges would have to accumulate without leaving the node. Neither effect has ever been observed, because nature conserves electrical charges. Kirchhoff’s current law states this fact concisely.

Kirchhoff’s Current Law (KCL): [Charge conservation]

The algebraic sum of the currents entering a node is zero.

This law must be read with the convention of reference directions in mind. When summing up the currents at a node, we account for incoming currents with a positive sign and outgoing currents with a negative sign. The opposite accounting works as well, if applied consistently. For example, in Figure 1.5, the sum of the currents is according to KCL:

Add \(I_3\) to both sides of the equation to see that outgoing current \(I_3\) is the sum of the incoming currents \(I_1 + I_2.\) Multiply both sides of the equation with \(-1,\) and we see that counting incoming currents as negative and outgoing currents as positive yields the same result, \(-I_1 - I_2 + I_3 = 0.\) Since KCL applies to the reference directions of the currents, the actual currents may still flow in the opposite direction. For instance, if we happen to measure currents \(I_1 = 5 A\) and \(I_3 = 2 A,\) then KCL tells us that \(I_2 = I_3 - I_1 = -3 A.\) Thus, current \(I_2\) is actually flowing out of the node rather than in.

The concept of a node in an electrical circuit is important. In fact, as used in KCL, node has a broader meaning than just a connection of wires, like those that we mark with a fat dot. Consider the circuits in Figure 1.6, two resistors in series on the left, and two parallel resistors on the right.

What is the relation between currents \(I_1\) and \(I_2\) in these two circuits? In the series composition on the left, we connect resistors \(R_x\) and \(R_y\) at node \(N_2.\) Applying KCL to node \(N_2,\) we find that \(I_x + I_y = 0,\) or \(I_x = -I_y.\) No surprise here, because our node is nothing but a dot that we attached to the wire. There can be only one current flowing in one direction through the wire. Whether we call it \(I_x\) or \(I_y\) does not matter. By the same argument, if \(I_x\) is the current through resistor \(R_x,\) then \(I_1\) is the same current, i.e. \(I_1 = I_x.\) Analogously, the current through \(R_y\) is \(I_y = I_2.\) Because \(I_x = -I_y,\) we conclude that \(I_1 = -I_2.\) Notice that we could have gained this insight by applying KCL to node \(N_1,\) the closed curve around \(R_x\) and \(R_y,\) directly: the sum of the currents entering \(N_1\) must be zero, i.e. \(I_1 + I_2 = 0.\)

For the parallel composition in Figure 1.6 on the right, we suspect that \(I_1 = -I_2\) as well, because this is the consequence of applying KCL to node \(N_1.\) The circuit contains two simple nodes, \(N_2\) and \(N_3.\) This is a more complex situation than the series composition. So, let’s double check whether KCL holds for node \(N_1.\) Applying KCL at nodes \(N_2\) and \(N_3,\) we find

To find the relation between \(I_1\) and \(I_2\) we can eliminate \(I_x\) and \(I_y\) algebraically. From the equation for \(N_2,\) we have \(I_x + I_y = I_1.\) Substituting in the equation for \(N_3,\) we obtain \(I_2 + I_1 = 0,\) which is the same equation that we obtain by applying KCL to node \(N_1.\) We have just verified that KCL applies to nodes that are closed curves through a circuit. In fact, KCL applies to nodes that are arbitrary closed surfaces in 3-dimensional space as well. A large node collapsed into a small dot has the appearance of a simple node and the same electrical behavior from the perspective of the surrounding circuit.

1.3.2. Kirchhoff’s Voltage Law¶

The second observation of Kirchhoff characterizes the forces in a loop. A loop is a closed path through a circuit that visits each element no more than once. First consider the fluid flow analogy in Figure 1.7 with a system of three water tanks connected via pipes. If the pump is off, the height of the water columns causes a balancing flow. Since \(h_1 > h_2,\) there will be a positive flow \(U_2.\) Also, since \(h_2 > h_3,\) flow \(U_3\) will be positive. If the pump is switched on, a positive flow \(U_1\) will replenish tank 1, i.e. increase \(h_1,\) while depleting tank 3, i.e. decreasing \(h_3.\)

The driving force behind the water flow is the hydrolic pressure caused by the height difference of neighboring water columns and of the pump. If we sum up the height differences along the loop, we find that the sum is zero:

Kirchhoff’s voltage law expresses the analogous effect for loops in electrical circuits.

Kirchhoff’s Voltage Law (KVL): [Energy conservation]

The algebraic sum of the voltages around a circuit loop is zero.

Figure 1.8 shows the circuit analogon to the water tank system in Figure 1.7. The circuit consists of a single loop with a voltage source, and three resistors. A voltage source is an idealized circuit element that generates constant voltage \(V\) with the annotated polarity, independent of the current flowing through it. We have chosen a clockwise reference direction for current \(I,\) and have annotated the polarities for the voltages across the resistors to decrease in the direction of the current. To form the sum of the voltages, assign a direction in which to traverse the loop, and account for device voltages in the direction of the loop as positive and voltages against the loop as negative. Our choice for the traversal direction is clockwise, as indicated by the blue arrow. The voltage decreases across each resistor in traversal direction, whereas the voltage increases across the voltage source. Therefore, the sum of the voltages is zero according to KVL:

Adding \(V\) to both sides shows that \(V = V_1 + V_2 + V_3,\) i.e. the driving force, the voltage source, produces voltage \(V\) that equals the sum of the voltage drops across the resistors. Thus, the electrical energy produced by the source is transformed into thermal energy by the three resistors. In other words, the circuit loop conserves energy by consuming the same amount of electrical energy as it produces. This insight is the crux behind KVL.[2]

The choice of the reference directions for voltages and currents, and the traversal direction of the loop does not affect the validity of KVL. It merely causes signs to change consistently. For example, had we chosen a counterclockwise traversal direction when applying KVL to the circuit in Figure 1.8, we would have obtained \(V - V_1 - V_2 - V_3 = 0.\) This equation is equivalent to the original KVL equation, as multiplication of both sides by \(-1\) reveals.

The concept of a loop in a circuit is easy. However, finding all loops of a circuit can be less than trivial. Consider the circuit in Figure 1.9.

The simple loops are shown on the left. Loops are simple if they do not cross wires.[3] Applying KVL to the three simple loops yields three equations:

We can form larger loops by combining these simple loops. Merging loops \(L_2\) and \(L_3\) yields loop \(L_4,\) and merging all three loops \(L_1,\) \(L_2,\) and \(L_3\) yields loop \(L_5.\) The corresponding KVL equations are:

The circuit has two more loops yet, shown on the right in Figure 1.9. Loop \(L_6\) is the result of merging loops \(L_1\) and \(L_2,\) and loop \(L_7\) merges loops \(L_1\) and \(L_3.\) Their KVL equations are:

The equations for loops \(L_1,\) \(L_2,\) and \(L_3\) relate the five voltages of the circuit to each other. From loop equations \(L_1\) and \(L_3\) we know that \(V_1 = V\) and \(V_3 = V_4.\) Furthermore, from loop \(L_2\) we can derive with the aid of \(L_1\) that \(V_2 = V_3 + V.\) Note that relative to this knowledge, the merged loop equations do not add any new information. For example, loop equation \(L_4\) is equivalent to \(L_2,\) if we employ \(L_3\) to substitute \(V_3\) for \(V_4.\) Analogously, loop equations \(L_5\) and \(L_6\) are equivalent to \(L_2\) by substituting \(V_1\) for \(V\) due to \(L_1.\) Moreover, equation \(L_7\) is equivalent to the sum of equations \(L_1\) and \(L_2.\) In general, we find that the simple loops contain all the relevant information about the voltages and energy distribution across a circuit. Nevertheless, KVL applies to all loops in a circuit.

Derive the node equations of KCL to determine the unknown currents in these circuits:

Deduce currents \(I_1\) and \(I_2\) in the 2-node circuit on the left and currents \(I_3,\) \(I_4,\) and \(I_5\) in the 3-node circuit on the right.

Consider the 2-node circuit first. We wish to determine current \(I_1\) flowing from the node on the left, call it \(N_1,\) to the node on the right, say \(N_2,\) and current \(I_2\) which exits node \(N_2.\) Node \(N_1\) has one current of \(5 A\) entering and four currents exiting. Since \(I_1\) is the only unknown current of \(N_1,\) applying KCL enables us to determine \(I_1\) by setting the sum of the currents to \(0\) or, to be mathematically precise, to \(0 A,\) because currents have unit Ampere:

Solving for \(I_1\) yields

Now that we know \(I_1,\) we find that \(I_2\) is the only unknown current of node \(N_2.\) The node equation for \(N_2\) due to KCL is:

Solving for \(I_2\) and substituting \(I_1 = -1 A\) yields

Next, we determine unknown currents \(I_3,\) \(I_4,\) and \(I_5\) of the 3-node circuit. KCL gives us three node equations, starting at the top node in clockwise direction:

The third equation is the only one with a single unknown, and permits computing \(I_5\):

Substituting \(I_5\) in the second equation yields \(I_4\):

Using the first equation, we obtain

Derive the loop equations of KVL to determine the unknown voltages in these circuits:

Deduce voltages \(V_1\) and \(V_2\) in the 2-loop circuit on the left and voltages \(V_3,\) \(V_4,\) and \(V_5\) in the 3-loop circuit on the right.

First, we deduce voltages \(V_1\) and \(V_2\) of the 2-loop circuit on the left. The circuit has two simple loops. Imagine we traverse the left loop in clockwise direction. The voltage source generates \(4 V\) in counterclockwise direction, whereas the reference directions of all three resistors point clockwise from high to low voltage. KVL yields the loop equation by forming the sum of the voltages, with those voltages negated that point against the loop direction, and setting the sum to \(0\) or, to be mathematically precise, to \(0 V,\) because voltages have unit Volt:

We rearrange the equation to obtain unknown voltage \(V_1\):

Knowing that \(V_1 = 0 V,\) we apply KVL to the simple loop on the right of the circuit to determine unknown voltage \(V_2.\) Let’s traverse the loop counterclockwise. Then the loop equation is:

so that

The circuit on the right has three simple loops. We determine voltages \(V_3,\) \(V_4,\) and \(V_5\) by applying KVL to each simple loop in clockwise direction, resulting in the three loop equations:

The first equation yields

the second equation

and substituting \(V_4\) in the third equation

You may verify that the resulting voltages fulfill KVL not only for the simple loops but all others as well.

Determine the voltages and currents of all voltage sources and resistors by applying Ohm’s law, KCL, and KVL.

Furthermore, verify that the circuit as a whole conserves energy, that is the sum of the energy consumptions of all devices is zero.

We begin the analysis of the circuit by introducing names for all unknown voltages and currents. Each of the five resistors is associated with a voltage, that we call \(V_1, V_2, \ldots, V_5.\) The circuit has two nodes, \(N_1\) and \(N_2,\) where three wires join. We denote the associated currents \(I_1,\) \(I_2,\) and \(I_3.\) The directions of all voltages and currents are chosen arbitrarily.

We apply KCL to node \(N_1,\) by counting entering currents \(I_1\) and \(I_2\) as positive and exiting current \(I_3\) as negative. Thus, we obtain node equation \(I_1 + I_2 - I_3 = 0,\) and we find that

If we apply KCL to node \(N_2,\) we obtain \(I_3 - I_1 - I_2 = 0,\) which is equivalent to the result for node \(N_1\) and, therefore, is not useful. The circuit has two simple loops, \(L_1\) and \(L_2,\) to each of which we apply KVL in clockwise direction:

The relationship between current and voltage of a resistor is given by Ohm’s law. We account for the directions by counting a current positive if it has the same direction as the voltage, otherwise we count the current as negative. Ohm’s law gives us one equation for each of the five resistors:

Substituting the resistor equations and the node equation into the loop equations yields two equations in two unknown currents \(I_1\) and \(I_2\):

Solving this system of equations yields currents:

Using the node equation we find \(I_3 = I_1 + I_2 = 0.538 A.\) Substituting these currents in the resistor equations yields the voltages:

Next, we verify these results by checking that the circuit conserves energy. Since voltage sources produce electrical energy and resistors consume electrical energy, we wish to know whether the energy transfer from the voltage sources to the resistors is confined to these devices, i.e. no energy is lost or accumulated over time. Hence, we verify whether the average energy produced per unit of time equals the average energy consumed per unit of time. In other words, the sum of the power consumptions of all devices must be zero, if we observe the passive sign convention. The power of a voltage source and of a resistor is the product of its voltage and current, \(P = V I.\) For the three voltage sources of the circuit, we count the currents negatively, because they point in the opposite direction as the voltages. Thus, we obtain the total produced power as a negative number:

Analogously, we find for the resistors:

Since the sum of the consumed and produced power is zero, the circuit conserves energy, as it should. Furthermore, we have verified the voltages and currents of our circuit analysis, because they confirm that the circuit conserves energy indeed.

1.4. Resistive Circuits¶

A resistive circuit consists of resistors, wires, and voltage sources. The laws of Ohm and Kirchhoff suffice to determine the voltages and currents through all of these devices. In the following, we analyze resistive circuits, and demonstrate how to exploit the gained knowledge by replacing complex with simpler equivalent circuits, and how to design circuits that divide voltages and currents.

1.4.1. Resistors in Series¶

We build larger circuits from smaller ones. One basic composition pattern is the series composition of two resistors. Figure 1.10 shows a circuit with a voltage source and two resistors in series.

Resistor \(R_1\) is connected to the voltage source at node \(N_1\) and to resistor \(R_2\) at node \(N_2,\) which is connected to the voltage source at node \(N_3.\) We analyze the circuit by applying KCL to the three nodes:

which tells us that \(I = I_1 = I_2.\) Not unexpectedly, the same current flows through all devices of the circuit. Next, we apply KVL to the only loop of the circuit:

At last, we invoke Ohm’s law, to obtain the relations between the resistor voltages and currents:

Substituting \(V_1\) and \(V_2\) into the KVL equation and using current \(I,\) we obtain

Observe that this equation has the form of Ohm’s law. If we interpret the sum \(R_1 + R_2\) as the resistance of a single resistor \(R_s = R_1 + R_2,\) then we can replace the resistors in series with a single resistor, and obtain an equivalent circuit shown in Figure 1.11. By KVL, the voltage across \(R_s\) is supply voltage \(V\) and, by Ohm’s law, the current is \(I = V/R_s = V/(R_1 + R_2),\) just as in the original circuit.

The idea of an equivalent circuit is useful for the analysis of larger circuits. In particular, a circuit with \(N\) resistors in series is equivalent to a circuit with a single resistance that is the sum of the series resistances:

The circuit in Figure 1.10 is a voltage divider that divides voltage \(V\) in direct proportion to the series resistances \(R_1\) and \(R_2.\) Given current \(I = V/(R_1 + R_2),\) we find the voltages across the resistors using Ohm’s law:

Thus, we can use two resistors in series to obtain two smaller voltages from a larger voltage. For example, we do not even have to know the current flowing through the circuit to find two resistors that halve voltage \(V\): choose \(R_1\) and \(R_2\) to be equal. Then, \(V_1 = R_1/(R_1 + R_1) = V/2\) and \(V_2 = R_2/(R_2 + R_2) = V/2,\) i.e. \(V_1 = V_2 = V/2.\)

Resistor 1: Resistor 2:

Explore the voltage divider by varying the resistances, and verify your findings algebraically:

- What are the voltages if the resistance ratio is \(R_1/R_2 = 1/2\)?

- What are the voltages if the resistance ratio is \(R_1/R_2 = 1/99\)?

- Which resistances cause \(I = 20 mA\) at ratio \(R_1/R_2 = 1\)?

1.4.2. Resistors in Parallel¶

The other basic composition pattern besides series composition is parallel composition. Figure 1.12 shows a circuit with two parallel resistors and a voltage source.

Both resistors \(R_1\) and \(R_2\) are connected to the voltage source at nodes \(N_1\) and \(N_2.\) By Ohm’s law, the voltage across \(R_1\) is \(V_1 = R_1 I_1,\) and the voltage across \(R_2\) is \(V_2 = R_2 I_2.\) To analyze the circuit, we first apply KVL to the two simple loops:

We find that \(V_1 = V_2 = V,\) i.e. the voltage across each of the resistors equals supply voltage \(V.\) Next, we apply KCL to node \(N_1\):

We replace \(I_1 = V_1/R_1\) and \(I_2 = V_2 / R_2\) according to Ohm’s law. Furthermore, since \(V_1 = V_2 = V,\) the node equation is equivalent to:

This equation has the form of Ohm’s law, if we interpret

as the resistance of a single resistor \(R_p.\) The equivalent circuit is shown in Figure 1.13.

The algebra above simplifies by using conductances instead of resistances. Let \(G_1 = 1/R_1\) and \(G_2 = 1/R_2,\) then Ohm’s law yields \(I_1 = G_1 V\) and \(I_2 = G_2 V,\) and the KCL equation for node \(N_1\) becomes:

Now, interpret \(G_p = G_1 + G_2\) as the conductance of the resistor in Figure 1.13, i.e. \(G_p = 1/R_p.\)

In general, if a circuit has \(N\) parallel resistors, it is equivalent to a circuit with a single conductance that is the sum of the parallel conductances:

or, in terms of resistances:

The circuit in Figure 1.12 is a current divider that divides current \(I\) in direct proportion to the conductances \(G_1\) and \(G_2,\) or in inverse proportion to their resistances \(R_1\) and \(R_2.\) From KCL and Ohm’s law, we know that

Now, express currents \(I_1\) and \(I_2\) in terms of \(I,\) \(R_1\) and \(R_2\):

These equations tell us that we can use two parallel resistors to obtain two smaller currents from a larger current. For example, to divide a current in half, use two resistors with equal resistances \(R_1 = R_2.\) Then, \(I_1 = R_2/(R_2+R_2) I = I/2\) and \(I_2 = R_1/(R_1+R_1) I = I/2,\) i.e. \(I_1 = I_2 = I/2.\)

Resistor 1: Resistor 2:

Explore the current divider by varying the resistances, and verify your findings algebraically:

- Which resistances cause \(I = 200 mA\) at ratio \(R_1/R_2 = 1\)?

- What are the currents if the resistance ratio is \(R_1/R_2 = 1/100\)?

- What are the currents \(I_1\) and \(I_2\) if the resistance ratio is \(R_1/R_2 = 1/2\) and \(I = 50 mA\)?

The current divider nourishes the widespread intuition that electricity follows the path of least resistance.

1.4.3. Resistor Networks¶

The concepts of voltage and current dividers are useful not only for the synthesis of circuits, but also for analyzing larger circuits with resistor networks. Example 1.7 illustrates how we can exploit the properties of series and parallel compositions for circuit analysis.

Consider the resistive circuit in Figure 1.14. We wish to determine voltage \(V_3\) across resistor \(R_3.\)

We could analyze the circuit by applying Ohm’s law, KCL and KVL, or, alternatively, derive an equivalent circuit that collapses the eight resistors into a single resistor. The idea of deriving an equivalent resistance is straightforward to apply. Iterate alternating steps of combining series and parallel resistors into equivalent resistors until the network is collapsed into a single resistance. Then, work backwards dividing voltages in series and currents in parallel compositions to determine the desired quantities.

Figure 1.15 below collapses the resistor network of Figure 1.14 into an equivalent resistance \(R_{30}.\) In the first step, we introduce equivalent resistances for all series compositions in the branches of the circuit in Figure 1.14:

In the second step, we replace parallel resistors \(R_{11},\) \(R_5,\) and \(R_{12}\) with equivalent resistance

In the third step, we collapse series resistors \(R_{10}\) and \(R_{20}\) into \(R_{30} = R_{10} + R_{20}.\) The resulting equivalent circuit enables us to determine current \(I = V/R_{30}\) that flows through the series-parallel resistor network as a whole.

Next, we work backwards through the transformations to determine \(V_3.\) Current \(I\) flows not only through \(R_{30}\) but also through each of the series resistors \(R_{10}\) and \(R_{20}.\) Expanding \(R_{20}\) into three parallel resistors, we find that current \(I\) divides into three branches. We are interested in the current through \(R_{11}\) only:

because the desired voltage \(V_3\) is the voltage induced by \(I_{11}\) across \(R_3\): \(V_3 = R_3 I_{11}.\) Substituting the intermediate expressions yields \(V_3\) as an unwieldy function of \(V\) and resistors \(R_1\) through \(R_8\):

Try deriving \(V_3\) using KCL, KVL, and Ohm’s law rather than calculating equivalent resistances to decide which method you prefer.

The series composition of resistors \(R_1\) and \(R_2\) has equivalent resistance:

\[R_s = R_1 + R_2 = 1\,k\Omega + 2\,k\Omega = 3\,k\Omega\,.\]The parallel composition of resistors \(R_1\) and \(R_2\) has equivalent conductance:

\[\begin{eqnarray*} G_p &=& G_1 + G_2 \\ \frac{1}{R_p} &=& \frac{1}{R_1} + \frac{1}{R_2} \\ &=& \frac{1}{1\,k\Omega} + \frac{1}{2\,k\Omega} \\ &=& \frac{3}{2\,k\Omega} \\ R_p &=& \frac{2}{3}\,k\Omega\,. \end{eqnarray*}\]We analyze the series-parallel composition of resistors inside-out. The series composition of \(R_1\) and \(R_2\) has equivalent resistance:

\[R_{1,2} = R_1 + R_2 = 3\,k\Omega\,.\]This resistance is in parallel with \(R_3.\) Their equivalent resistance is

\[R_{1,2,3} = \frac{R_{1,2}\,R_3}{R_{1,2} + R_3} = \frac{3}{2}\,k\Omega\,.\]This resistance is in series with \(R_4.\) The resulting equivalent resistance is

\[R_{sp} = R_{1,2,3} + R_4 = 2\,k\Omega\,.\]

Audio amplifiers use a potentiometer to control the volume of the loudspeaker. A potentiometer is a voltage divider that consists of a resistor \(R\) with an adjustable tap to partition \(R\) into \(R_1\) and \(R_2\) such that \(R = R_1 + R_2.\) The audio amplifier supplies output voltage \(V_a\) to the potentiometer, and the volume control taps voltage \(V_s\) for the speaker amplifier. The larger \(V_s,\) the louder is the sound produced by the speaker.

Plot voltage \(V_s\) as a function of the potentiometer position represented by \(R_2.\) Assume the speaker amplifier has an input resistance of \(50 \Omega,\) the potentiometer has resistance \(R = 1 k\Omega,\) the tap permits adusting \(R_2\) within range \(0 \Omega \le R_2 \le R,\) and the audio amplifier supplies voltage \(V_a = 2 V.\)

The circuit diagram on the right shows the potentiometer with input voltage \(V_a = 2V\) and the speaker amplifier replaced by its input resistance of \(50 \Omega.\) We wish to derive \(V_s\) as a function of \(R_2.\)

We perform a circuit analysis. We know that \(R = R_1 + R_2\) and \(R = 1 k\Omega.\) Since we treat \(R_2\) as a free variable that represents the potentiometer position, we express \(R_1\) as a function of \(R_2\):

Voltage \(V_s\) drops off both resistances \(R_2\) and the \(50 \Omega\) input resistance of the speaker amplifier. To simplify the circuit, we replace these two parallel resistors with their equivalent resistance

Now, series resistors \(R_1\) and \(R_p\) form a vanilla voltage divider. From Example 1.5 we know that

Substituing \(R_1\) and \(R_p,\) we find \(V_s\) as a function of \(R_2\):

The plot shows \(V_s\) as a function of \(R_2\):

Voltage \(V_s\) increases monotonically in \(R_2.\) However, it increases nonlinearly. This behavior offers the human user quite a natural feel. The potentiometer acts much more sensitive to changes at low volumes than at high volumes, giving you finer control over low volumes.

We demonstrate how to determine the equivalent resistance if two terminals span a resistor network that is a series-parallel composition, i.e. the network is constructed by repeated application of series or parallel composition of series-parallel subnetworks. First we redraw the network to expose the series and parallel compositions and, second, we collapse the network into a single resistor by step-wise replacement of series or parallel compositions with equivalent resistances. The key is to redraw the circuit so that we can easily see which compositions are series and which are parallel.

We begin with the equivalent resistance between terminals A and C. Remove terminals B and D, and imagine you pull terminal A to the left and terminal C to the right. Then, the circuit resembles this schematic:

This schematic shows that the network between terminals A and C is a parallel composition of three subnetworks. The top and bottom subnetworks are series compositions of two resistances, respectively, and the subnetwork in the middle is trivial because it consists of a single resistor only. We replace the simple series compositions first. The equivalent resistance of \(R_1\) and \(R_2\) is:

and, analogously:

Proceding with the parallel composition of \(R_{1,2},\) \(R_5,\) and \(R_{3,4},\) we form the sum of the reciprocals and obtain resistance \(R_{A\text{-}C}\) as a function of resistances \(R_1, \ldots, R_5\):

In the special case where all resistances are equal, for example \(R_1 = R_2 = \ldots = R_5 = R = 10 k\Omega,\) the expression for \(R_{A\text{-}C}\) simplifies dramatically to

Next, we consider the equivalent resistance between terminals A and B. We remove terminals C and D and redraw the circuit imagining we pull terminal A to the left and terminal B to the right:

The circuit is a series-parallel composition of resistors. We compute the equivalent resistance by replacing subcircuits, working inside-out. We note that \(R_3\) and \(R_4\) are composed in series, and replace the two resistors with equivalent resistance \(R_{3,4} = R_3 + R_4.\) Now, \(R_5\) and \(R_{3,4}\) are composed in parallel. We replace the parallel composition with equivalent resistance \(R_{3,4,5},\) which we compute by adding the reciprocals:

At this point, we note that \(R_{3,4,5}\) and \(R_2\) form a series composition. Thus, we replace the bottom branch of the circuit with equivalent resistance \(R_{2,3,4,5} = R_{3,4,5} + R_2.\) This leaves us with a parallel composition of \(R_1\) and \(R_{2,3,4,5},\) and equivalent resistance

For comparison, in the special case where where all resistances are equal to \(R = 10 k\Omega,\) the expression for \(R_{A\text{-}B}\) simplifies to

The resistance between terminals B and D requires a circuit analysis with KCL, KVL, and Ohm’s law, because the resistor network is not a series-parallel composition. No matter how you push or pull, resistor \(R_5\) forms a bridge between the two parallel branches \(B\text{-}R_1\text{-}R_3\text{-}D\) and \(B\text{-}R_2\text{-}R_4\text{-}D\) that cannot be generated with a series or parallel composition. The solution of the circuit analysis (try it yourself!) is:

Again, for comparison, in the special case where where all resistances are equal to \(R = 10 k\Omega,\) the expression for \(R_{B\text{-}D}\) simplifies to

What are the equivalent resistances between any of the other terminal pairs?

You have a voltage source with \(6 V\) and an unlimited supply of \(10 k\Omega\) resistors. Design resistive circuits to generate voltage \(V_a = 2 V,\) \(V_b = 3 V,\) \(V_c = 4 V,\) and \(V_d = 5 V,\) respectively.

Our plan is to design voltage divider circuits, because each of the desired voltages is less than supply voltage \(V = 6 V.\) We pick the simplest voltage first, \(V_b = 3 V,\) because \(V_b\) is exactly half of \(V.\) Analogous to Example 1.5, we compose two resistors \(R_1\) and \(R_2\) in series, where \(R_1 = R_2 = R = 10 k\Omega.\) Then, we can tap \(V_b\) off either resistor, because

The corresponding voltage divider circuit is shown on the left:

Next, we design a circuit to divide \(V = 6V\) down to \(V_a = 2V.\) We note that \(V_a\) is one third of \(V,\) and observe in the corresponding voltage divider equation

that we wish to determine \(R_x\) and \(R_y\) such that

Simplify this equation, and we find the equivalent condition \(R_y = 2 R_x.\) This condition is easy to fulfill: if we choose \(R_x = R,\) then \(R_y = 2 R,\) which we implement as a series composition of two resistors with resistance \(R.\) The resulting voltage divider circuit consists of three series resistors, as shown in the middle of the figure above. Note that each of the three resistors has a voltage drop of \(2 V\) or one third of \(6 V.\) Thus, we can tap \(V_a = 2 V\) off each of the resistors. Also note that this voltage divider circuit can be used to generate \(V_c = 4 V\) as well, because \(V_c = 2 V_a.\) Thus, we obtain \(V_c\) at the terminals of the series composition of two resistors, either \(R_1\) and \(R_2\) because \(V_1 + V_2 = 4 V\) or \(R_2\) and \(R_3\) because \(V_2 + V_3 = 4 V.\)

Voltage \(V_d = 5 V\) can be generated with an analogous argument as \(V_a.\) Since \(V_d/V = 5/6,\) we deduce from the voltage divider equation that \(R_x = 5 R_y.\) Therefore, if we choose \(R_y = R,\) then \(R_x = 5 R,\) which we could implement with six series resistors of resistance \(R.\) An alternative circuit derives from the voltage divider equation by choosing \(R_x = R.\) Then, \(R_y = R / 5,\) which we can implement with five parallel resistors of resistance \(R\) because the equivalent resistance \(R_p\) is

The corresponding voltage divider circuit is shown on the right in the figure above.

1.5. RC Circuits¶

In this section we introduce the capacitor and discuss RC circuits, circuits with resistors and capacitors. The usefulness of RC circuits unfolds when voltages and currents change over time. Then, RC circuits exhibit more interesting behavior than resistive circuits, and require mathematical tools from calculus for transient analysis.

1.5.1. The Capacitor¶

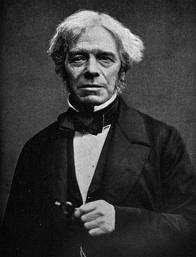

(1791-1867)

A capacitor is an electrical device with capacitance \(C.\)[4] The unit of capacitance is the Farad, \(1 F = 1 C / V,\) i.e. one Coulomb per Volt, in honor of the English physicist Faraday.

Capacitors store energy in an electrical field. The charge \(q\) in the capacitor is proportional to the voltage \(v\) across the field:

A capacitor consists of a dielectric insulator sandwiched between two conducting plates. Dielectrics are materials that do not conduct electric current but polarize in an electrical field, e.g. porcelain or oil. The capacitance of a capacitor is

where \(A\) is the area of the plates, \(d\) is the thickness of the dielectric, and \(\epsilon\) is a material constant of the dielectric. The larger a capacitor, the more charge it can store, and the larger is its capacitance.

When applying a constant voltage \(v\) to a capacitor, it behaves like an insulator, because the dielectric isolates the terminals. No current flows through the capacitor. However, if the voltage varies over time, the capacitor serves as an energy reservoir. The time dependence makes the behavior of a capacitor much harder to describe than a resistor but the usefulness of its properties are worth the effort.

Assume voltage \(v(t)\) across a capacitor with capacitance \(C\) varies over time \(t.\) Then, charge \(q(t)\) on the capacitor varies proportionally:

Since current is the change of charge over time, \(i(t) = d q(t) / dt,\) the current through the capacitor is

Alternatively, we use the integral form to express \(v(t)\) as a function of \(i(t)\):

The energy stored in the capacitor at time \(t\) is the integral of the power consumption over time:

Here, we assume that the integration constant is zero, as it would be if the initial voltage were zero. Unlike a resistor, which dissipates electrical energy as heat, a capacitor stores electrical energy. At any point in time, the amount of energy stored in a capacitor represents the history of changes accumulated by the integral. In contrast, the energy consumed by a resistor is instantaneous and independent of the history. Therefore, capacitors enable us to build memories whereas resistors alone do not.

1.5.2. Capacitor Networks¶

The two basic types of composition, series and parallel, are useful for constructing and analyzing larger capacitor networks. Figure 1.17 shows two capacitors in series and a voltage source.

To analyze the series composition, we observe that current \(i(t)\) flows through both capacitors \(C_1\) and \(C_2.\) Applying KVL to the circuit loop, we find that

Observe that the last expression gives the voltage across a single capacitor with capacitance \(C_s,\) such that

Thus, the equivalent capacitance of two capacitors in series is calculated analogously to the equivalent resistance of two parallel resistors. In general, the equivalent capacitance \(C_s\) of \(N\) capacitors in series is

The parallel composition of two capacitors is shown in Figure 1.18. We notice that the voltages across the capacitors are \(v_1 = v_2 = v.\) Applying KCL, we obtain:

Observe that this expression characterizes the current through a single capacitor with capacitance \(C_p,\) where

The capacitances of two parallel capacitors are additive. This is consistent with the geometric intuition that the areas of capacitor plates add up when joined. In general, the equivalent capacitance \(C_p\) of \(N\) parallel capacitors is the sum

The concept of equivalent capacitances enables us to simplify larger capacitive networks without need for calculus, analogous to the simplification of resistive networks in Example 1.7.

1.5.3. Steady State vs Transients¶

We say that a circuit is in steady state if all voltages and currents are stable.[5] For example, when the resistive circuit in Figure 1.19 is in steady state, the resistor conducts current \(i\) according to Ohm’s law. According to KVL, we have \(v_R = V,\) and

Since currents and voltages do not change over time in steady state, we emphasize the situation by using upper-case letters \(I = i(t)\) and \(V = v(t).\)

The steady state behavior of the capacitive circuit in Figure 1.20 is even simpler than that of the resistive circuit. By KVL, we have \(v_C = V.\) Since the voltage across the capacitor is constant, the capacitor isolates its terminals, such that no current can flow. Therefore, we conclude that the steady state current is

independent of the magnitude of capacitance \(C.\)

The interesting behavior of the capacitive circuit is not its steady state but its transient behavior. When the voltage of the voltage source varies over time, e.g. if we could switch the voltage on or off, the circuit reacts with a transient response. We can describe the transient response of a circuit using methods from calculus. In the next section, we perform the transient analysis of an RC circuit.

1.5.4. RC in Series¶

One of the simplest RC circuits is the series composition of a resistor and a capacitance, as shown in Figure 1.21. In steady state, when the voltage source supplies constant voltage \(V,\) the capacitor acts like an insulator. No current can flow through the circuit loop, including the resistor. Therefore, by Ohm’s law,

because \(I = 0\) in steady state, and by KVL

To study the transient behavior of the RC circuit, we introduce a new device, a switch, that we can open or close. The open switch disconnects its terminals, whereas the closed switch behaves like a wire that connects the terminals. Figure 1.22 extends the circuit of Figure 1.21 with a switch. We assume that the switch is open initially, and we close the switch at time \(t=0.\) We analyze the time dependent response of the circuit to the closing of the switch.

\(t < 0\): Switch is open.

The open switch prevents a current from flowing through the circuit. Therefore, \(i(t) = 0\) and, by Ohm’s law, \(v_R(t) = R\, i(t) = 0.\) Since the \(+\) terminal of the capacitor floats, i.e. is not connected to any device that could induce a particular voltage, we assume that \(v_C(t) = 0.\)

\(t \ge 0\): Switch is closed.

We apply KVL to the circuit loop in clockwise direction:

\[R i(t) + \frac{1}{C} \int_0^t i(\tau) d\tau - V = 0\,,\]and transform the integral equation into a differential equation by taking the derivative in \(t\):

\[R \frac{d i(t)}{dt} + \frac{1}{C} i(t) = 0\,.\]This equation models the time dependent behavior of current \(i\) through the RC circuit. Dividing both sides by \(R\) casts the equation into the form of a homogeneous differential equation with constant coefficients, actually one constant coeffient \(1/RC\):

\[\frac{d i(t)}{dt} + \frac{1}{R C} i(t) = 0\,.\]Recall from calculus that such an equation has the general solution

\[i(t) = k_1 + k_2 e^{-k_3 t}\,,\]where \(k_1,\) \(k_2,\) and \(k_3\) are constants that are determined by the initial condition at time \(t=0\) and the steady state, where \(t \rightarrow \infty.\)

\(t \rightarrow \infty\): steady state

In steady state with a closed switch, the circuit behaves as analyzed above for Figure 1.21 already. The capacitor acts like an insulator, so that \(i(\infty) = 0.\) Because \(e^{-k_3 t} \rightarrow 0\) for \(t \rightarrow \infty,\) the steady state enables us to determine constant \(k_1\):

\[\begin{split}\begin{eqnarray*} i(\infty) &=& k_1 + k_2 \cdot 0 \\ \Leftrightarrow\qquad k_1 &=& 0\,. \end{eqnarray*}\end{split}\]\(t = 0\): initial condition

The switch has just closed. Therefore, no charges can have accumulated in the capacitor yet, so that \(v_C(0) = 0.\) Hence, by KVL, source voltage \(V\) equals the voltage across the resistor, \(v_R(0) = V.\) This voltage induces instantaneous current \(i(0) = V/R\) through the resistor. We call this current \(I_0 = V/R\) at \(t=0\) the initial current. Since \(e^0 = 1,\) we can determine constant \(k_2\):

\[\begin{split}\begin{eqnarray*} i(0) &=& k_2 \cdot 1 \\ \Leftrightarrow\qquad k_2 &=& \frac{V}{R}\,. \end{eqnarray*}\end{split}\]It remains to determine constant \(k_3.\) To that end, we substitute \(i(t) = I_0 e^{-k_3 t}\) in the differential equation. Applying the chain rule of differentiation, we find that

\[\frac{d i(t)}{d t} = - k_3 I_0 e^{-k_3 t}\,,\]and the differential equation yields

\[\begin{split}\begin{eqnarray*} - k_3 I_0 e^{-k_3 t} + \frac{1}{RC} I_0 e^{-k_3 t} &=& 0 \\ k_3 &=& \frac{1}{RC}\,. \end{eqnarray*}\end{split}\]Thus, we have found the solution for current \(i(t)\) when \(t \ge 0\):

\[i(t) = I_0 e^{-\frac{t}{RC}} = \frac{V}{R} e^{-\frac{t}{RC}}\,.\]We call constant \(RC,\) the product of the resistance and capacitance, the time constant of the circuit, because it determines how fast the current approaches its steady state value \(i(\infty) = 0.\)

Now that we know current \(i(t),\) we can deduce voltage \(v_C(t)\) across the capacitor:

\[\begin{split}\begin{eqnarray*} v_C(t) &=& \frac{1}{C} \int_0^t i(\tau) d \tau \\ &=& \frac{V}{RC} \int_0^t e^{-\frac{\tau}{RC}} d \tau \\ &=& V \bigl(1 - e^{-\frac{t}{RC}}\bigr)\,. \end{eqnarray*}\end{split}\]

The interactive graph Figure 1.23 explores the dependence of \(i(t)\) and \(v_C(t)\) on time constant \(RC,\) assuming that \(I_0 = 1 A\) and \(V = 1 V.\) At time \(t=0\) the current jumps from 0 to \(I_0,\) and then decreases exponentially as time passes. This current charges the capacitor. Therefore, voltage \(v_C(t),\) which is initially 0, increases when the switch closes at time \(t=0,\) and approaches \(V = 1 V\) within a time period proportional to \(RC.\) At time \(t=0,\) a larger current increases the capacitor voltage faster than the smaller current at \(t \gg 0.\) The bottomline is that the time period the current takes to charge the capacitor is proportional to \(RC.\)

Time constant RC: 1

Figure 1.23: Capacitor voltage and current as a function of time. Vary time constant RC to see at which time \(t\) the capacitor voltage reaches \(V = 1 V,\) effectively completing the transition that starts with closing the switch at time \(t = 0.\)The series composition of capacitors \(C_1\) and \(C_2\) has equivalent capacitance \(C_s\):

\[\begin{eqnarray*} \frac{1}{C_s} &=& \frac{1}{C_1} + \frac{1}{C_2} \\ &=& \frac{1}{10\,pF} + \frac{1}{20\,pF} \\ &=& \frac{3}{20\,pF} \\ C_s &=& \frac{20}{3}\,pF\,. \end{eqnarray*}\]The parallel composition of capacitors \(C_1\) and \(C_2\) has equivalent capacitance:

\[C_p = C_1 + C_2 = 10\,pF + 20\,pF = 30\,pF\,.\]We analyze the series-parallel composition of capacitors inside-out. The series composition of \(C_1\) and \(C_2\) has equivalent capacitance:

\[C_{1,2} = \frac{C_1\,C_2}{C_1 + C_2} = 5\,pF\,.\]This capacitance is in parallel with \(C_3.\) Their equivalent capacitance is:

\[C_{1,2,3} = C_{1,2} + C_3 = 20\,pF\,.\]This capacitance is in series with \(C_4.\) The resulting equivalent capacitance is:

\[C_{sp} = \frac{C_{1,2,3}\,C_4}{C_{1,2,3} + C_4} = 10\,pF\,.\]

Compute the equivalent capacitances of these capacitive circuits, assuming each capacitor has a capacitance of \(C = 6 pF\):

We observe that all four capacitive circuits are series-parallel networks, that we discuss in Exercise 1.12 in the context of resistor networks as well.

Consider the series composition of three capacitors given in circuit (a). From our study of capacitor networks we know that the equivalent capacitance \(C_a\) of the series composition is

Therefore, we find for \(C = 6 pF\) that

Circuit (b) shows a parallel composition of three capacitors. As discussed in Section Capacitor Networks their capacitances add up to equivalent capacitance

Circuit (c) is a parallel composition of two branches, where the left branch is a series composition. We begin by replacing the series composition with its equivalent capacitance

Next, we determine equivalent capacitance \(C_c\) of the parallel composition:

This is the equivalent capacitance of circuit (c).

Circuit (d) is a series composition, where the bottom subnetwork forms a parallel composition. Again, we begin by replacing the parallel composition with its equivalent capacitance:

Then, the equivalent capacitance \(C_d\) of the series composition is

We find that the four capacitive networks have distinct equivalent capacitances. From a constructive point of view, if you happen to have a supply of capacitors with \(C = 6 pF,\) you can combine three capacitors in a series-parallel fashion to obtain capacitances of \(2 pF,\) \(4 pF,\) \(9 pF,\) and \(18 pF.\)

Consider the capacitors below, assuming the dielectric has permittivity \(\epsilon = 8 \times 10^{-10} F/m.\) The dielectric of capacitor (a) shall have thickness \(d = 8 {\mathring A}.\) Unit Angstrom is defined as \(1 {\mathring A} = 10^{-10} m.\) Furthermore, the length of capacitor (a) shall be \(L = 1 \mu m\) and its width \(W = 1 \mu m.\)

Determine the capacitances of the three capacitors.

The capacitance of a capacitor with plate area \(A = L W\) is \(C = \epsilon L W / d.\) Therefore, to determine capacitance \(C_a\) of capacitor (a), all we need to do is plug in the numbers, and obtain:

Analogously, we can determine capacitance \(C_b\) of capacitor (b) by plugging the numbers into the capacitance formula. However, notice that capacitor (b) has the same dielectric thickness as capacitor (a), and the plate area matches that of an array of \(3 \times 2\) capacitors (a). Thus, we may view capacitor (b) as a parallel composition of six copies of capacitor (a):

Since the equivalent capacitance of parallel capacitances is their sum, we find that

Capacitor (c) has four times the plate area of capacitor (a) and its dielectric is twice as thick. Therefore, we may derive capacitance \(C_c\) from \(C_a\):

such that \(C_c = 2 C_a = 2 pF.\)

The circuit below extends Figure 1.22 with a switch position that enables us to bypass the voltage source. Assume that the circuit is in the steady state after the transition discussed above, and analyze what happens after throwing the switch downward.

Before throwing the switch, the circuit has the same topology as the circuit in Figure 1.22 with the switch closed. We found above that the steady state of that circuit at \(t \rightarrow \infty\) is \(i(\infty) = 0,\) \(v_R(\infty) = 0,\) and \(v_C(\infty) = V.\) Now, we assume that our modified circuit assumes this steady state as start state, and we throw the switch downward at \(t = 0.\) Thus, for the new switch transition of interest we assume that \(i(t) = 0,\) \(v_R(t) = 0,\) and \(v_C(t) = V\) for \(t < 0.\)

After throwing the switch downward at \(t=0,\) the voltage source is disconnected, and the active part of the circuit consists of the single loop shown on the right. In the following, we analyze this circuit for \(t \ge 0.\)

Apply KVL in clockwise direction to obtain loop equation

Taking the derivative yields the differential equation

This is the same differential equation we found during the analysis of the switch transition above. However, we expect a different solution, because the initial conditions differ. In particular, the capacitor stores charges such that voltage \(v_C(0) = V,\) i.e. the inital capacitor voltage equals the voltage of the disconnected voltage source. Assuming as above that the loop current has the general solution

we conclude that \(k_1 = 0\) because \(i(\infty) = 0.\) Initial condition \(v_C(0)=V\) enforces \(v_R(0) = -V,\) or KVL would not hold at \(t = 0.\) We conclude that the initial loop current is the current through the resistor, so that

The time constant of the series composition of resistor and capacitor is \(RC,\) so that constant \(k_3\) must be \(k_3 = 1/RC.\) In summary, we have found that loop current

flows in the opposite direction of the reference direction. The capacitor acts as current source, and discharges itself through the resistor. Furthermore, we can deduce voltage \(v_C(t)\) across the capacitor directly from KVL without integration:

The capacitor voltage decreases exponentially from \(v_C(0) = V\) to \(v_C(\infty) = 0.\)

1.6. Transistors¶

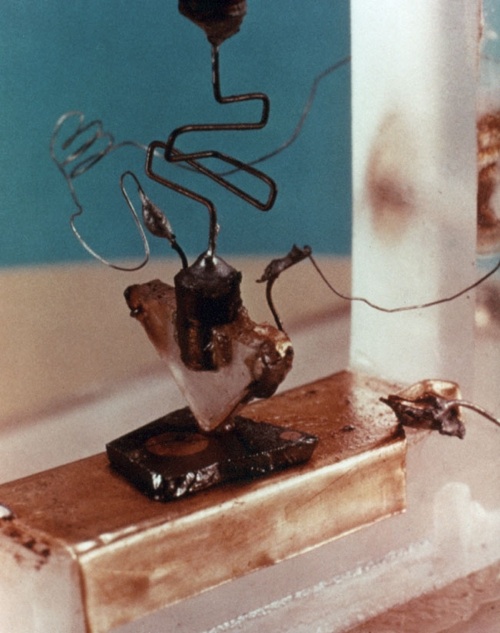

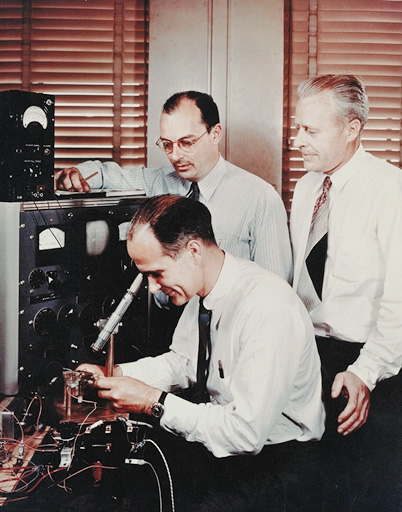

A transistor is a switching device that enables us to control the flow of current in one circuit by means of the voltage in another circuit. The first transistor prototype is shown in Figure 1.24. It was built at AT&T’s Bell Laboratories in 1947 by Bardeen, Brattain, and Shockley, see Figure 1.25. Today, transistors exist in various technologies of different types. We discuss the most common kind, the MOSFET, metal-oxide-semiconductor field-effect transistor, or MOS transistor for short. We are less interested in the inner workings of transistors but their common functionality and timing behavior. To that end, we study a simplistic switch model and a more detailed RC model of the MOS transistor.

Figure 1.25: The inventors of the transistor: William Shockley (front), John Bardeen (left), and Walter Brattain (right).

1.6.1. MOS Transistors¶

The name MOS transistor refers to the layer structure in which transistors are built: metal on top, silicon dioxide in the middle, and a semiconductor at the bottom. MOS transistors come in two types, the nMOS and the pMOS transistor, shown in Figure 1.26.

MOS transistors are devices with three terminals: gate, source, and drain. The silicon dioxide \(\text{(SiO}_2\text{)}\) serves as dielectric layer of a capacitor with the gate metal as the top plate and the silicon substrate as the bottom plate. In the nMOS transistor, the n-type source and drain regions contain donor atoms, capable of donating electrons to an electrical current, whereas the substrate is of p-type, i.e. it contains acceptor atoms that donate positive charges (holes). In the pMOS transistor, the types of the regions are reversed.